Altera Cyclone® IV FPGAs

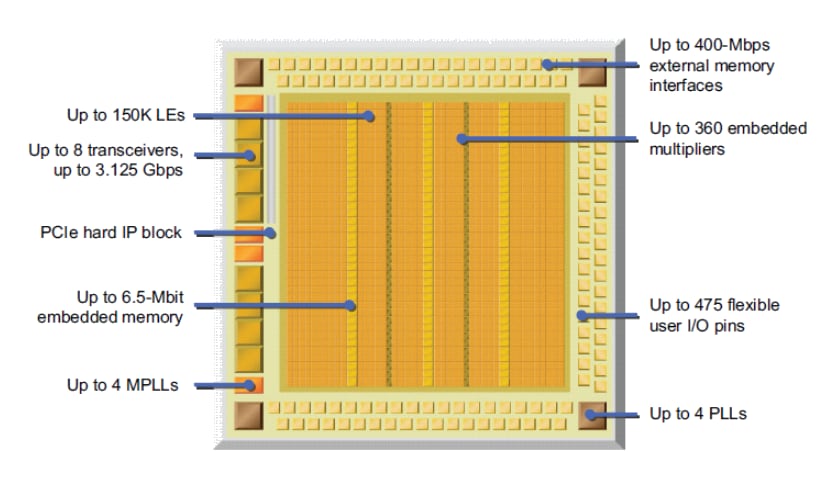

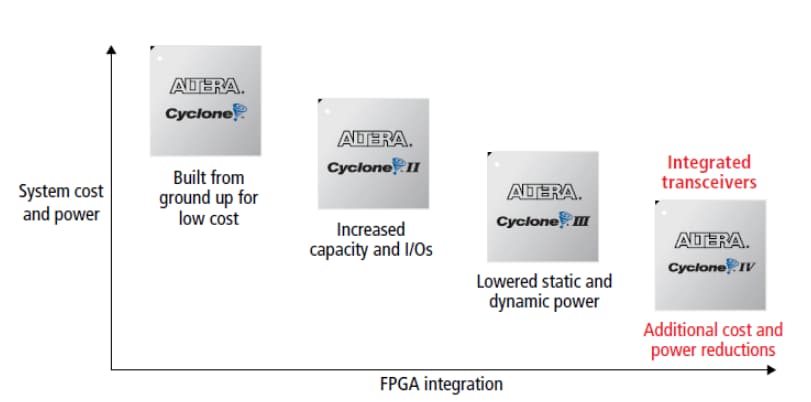

Altera Cyclone® IV FPGAs extend the power- and cost-optimized Cyclone FPGA series that is engineered for very low cost and power consumption, making the devices ideal for high-volume, cost-sensitive applications across industries such as wireless, broadcast, industrial, and retail electronics. Cyclone IV devices are available in two variants: the Cyclone IV E (FPGA fabric and I/O optimized for low power and high functionality) and the Cyclone IV GX, which adds low-power 3.125Gbps transceiver inputs and outputs supporting multiple serial channel protocols and PCIe 1.0 x1/x2/x4 lane capabilities.

These Altera FPGAs provide a balance of simple logic, memory, DSP/AI compute engines, along with an abundance of general-purpose I/Os (GPIOs) and transceiver I/O to support efficient protocol bridging in power-sensitive, cost-sensitive, and high-volume applications. Providing power and cost savings, without sacrificing performance, along with a low-cost integrated transceiver option, Cyclone IV devices are ideal for low-cost, small-form-factor applications in the wireless, wireline, broadcast, industrial, consumer, and communications industries.

These FPGAs offer up to eight transceiver I/O channel pairs, and each transceiver channel pair consumes only 150mW, ensuring low-power operation even for high-speed serial I/O protocols. Additionally, the robust and configurable DSP capabilities make these devices capable of handling small AI workloads like Tiny ML and other convolutional neural networks, in addition to traditional DSP algorithms like FIR filters and FFTs used in image and signal processing.

Features

- Two variants

- Cyclone IV GX FPGAs with integrated 3.125Gbps transceiver I/Os for high-bandwidth applications

- Cyclone IV E FPGAs for a wide spectrum of general logic, control plane, and other embedded control applications

- Low-cost, low-power FPGA fabric

- Up to 150,000 simplified 4-input Look-Up-Table (LUT)-based logic elements

- Up to 6.3Mb of embedded high-speed, configurable SRAM memory

- Up to 360 configurable DSP blocks

- Up to 528 GPIOs

- Up to 8x transceiver I/O channel pairs

- Support for Nios® V 32-bit soft IP, embedded RISC-V-based processors

- Offered in commercial and industrial temperature grades

- Additional GX features

- Up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- Wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5Gbps)

- Gigabit Ethernet (1.25Gbps)

- CPRI (up to 3.072Gbps)

- Up to eight high-speed transceivers that provide:

Applications

- Broadcast

- Consumer

- Industrial

- Wireless

- Wirelines

Design Support

- To keep development costs low, Altera provides free, no-cost licenses for the following software tools:

Integration Chart

Architectural Features