## リアルタイムクロック付き 1-Mbit (128 K × 8) シリアル (SPI) nvSRAM

### 特長

- 1 M ビットの不揮発性スタティック RAM (nvSRAM)

- 128K × 8 としてメモリを内部的に編成

- QuantumTrapの不揮発性要素へのSTORE処理は、電源オフ時に自動的に実行 (AutoStore) できる他、SPI命令 (ソフトウェア STORE) または HSB ピン (ハードウェア STORE) を使用してユーザーが明示的に実行することも可能

- SRAMへのRECALL処理は、パワーアップ (パワーアップ RECALL) または SPI命令 (ソフトウェア RECALL) によって実行

- パワーダウン時に小容量コンデンサにより、自動的に STORE 処理

- 高い信頼性

- 回数に制限のないリード、ライト、RECALL サイクル

- QuantumTrapに対する 100 万回の STORE サイクル

- データ保存期間 : 85°C で 20 年

- リアルタイムクロック (RTC)

- フル機能 RTC

- ウオッチドッグタイマ

- プログラム割り込みクロックアラーム

- バックアップ電源異常表示

- プログラム周波数の方波出力 (1Hz, 512Hz, 4096Hz, 32.768kHz)

- RTC コンデンサまたはバックアップバッテリ

- 0.45µA(代表値)のバックアップ電流

- 40MHzおよび104MHzの高速シリアル周辺インターフェイス (SPI)

- 40MHzのクロック速度 SPI はゼロサイクル遅延で書き込みおよび読み取り

- 104MHzのクロック速度 SPI 書き込みおよび読み取り (特別な高速読み取り命令を使用)

- SPI モード 0 (0, 0) およびモード 3 (1, 1) をサポート

- 特別機能への SPI アクセス

- 不揮発性 STORE/RECALL

- 8 バイトのシリアル番号

- メーカー ID および製品

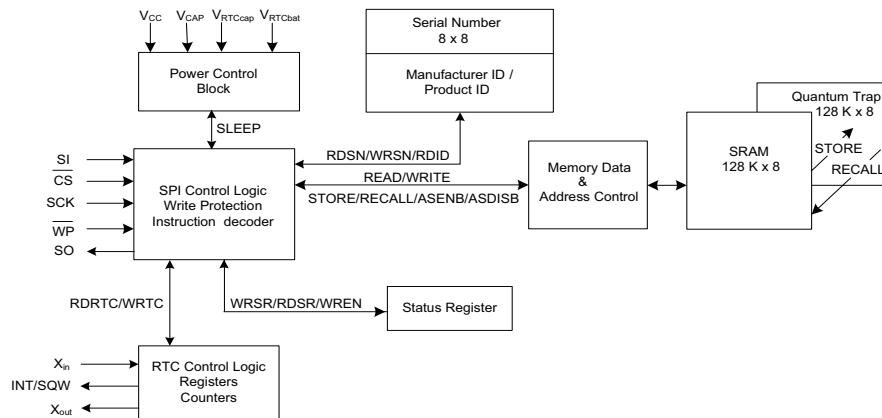

### ロジックブロック ダイヤグラム

#### 注

1. このデバイスは文書全ページで nvSRAM と示されています。

### □ スリープモード

### ■ 書き込み保護

- 書き込み保護ピン (WP) を使ったハードウェアによる保護

- 書き込みディスエーブル命令を使用したソフトウェアによる保護

- アレイの 1/4、1/2、または全体を対象としたソフトウェアブロック保護

### ■ 低消費電力

- 40MHz動作で平均 3mA のアクティブ電流

- スタンバイモードの平均電流 250µA

- スリープモードの電流 8µA

### ■ 業界標準の構成

- 動作電圧 :

- CY14C101PA:  $V_{CC}=2.4V \sim 2.6V$

- CY14B101PA:  $V_{CC}=2.7V \sim 3.6V$

- CY14E101PA:  $V_{CC}=4.5V \sim 5.5V$

- 工業用温度

- 16 ピン小型外形集積回路 (SOIC) パッケージ

- RoHS 準拠

### 概要

サイプレスの CY14X101PA は、1 Mbit nvSRAM<sup>[1]</sup> にフル機能の RTC を組み合わせ、シリアル SPI インターフェイスを持つモノリシック集積回路とした素子です。このメモリは、128K ワード × 8 ビットで編成されています。組み込み不揮発性要素には、QuantumTrap 技術が組み込まれており、世界でも最高レベルの信頼性を誇る不揮発性メモリを作り上げます。回数に制限のない読み取りと書き込みサイクルを SRAM で可能にする一方、高い信頼性を提供する不揮発性データ記憶域を QuantumTrap セルで実現しています。SRAM から不揮発性要素へのデータ転送 (STORE オペレーション) は、パワーダウン時に自動的に実行されます。パワーアップ時には、不揮発性メモリから SRAM にデータが復元されます (RECALL オペレーション)。STORE 効果と RECALL オペレーションは、いずれも SPI 命令を使用してユーザーが開始することができます。

## 目次

|                                     |    |

|-------------------------------------|----|

| ピン配列 .....                          | 3  |

| ピン機能 .....                          | 3  |

| 動作説明 .....                          | 4  |

| SRAM 書き込み .....                     | 4  |

| SRAM 読み込み .....                     | 4  |

| STORE 動作 .....                      | 4  |

| AutoStore 処理 .....                  | 4  |

| ソフトウェア STORE 動作 .....               | 5  |

| ハードウェア STORE 動作および HSB ピン動作 .....   | 5  |

| RECALL 動作 .....                     | 5  |

| ハードウェア RECALL (パワーアップ) .....        | 5  |

| ソフトウェア RECALL .....                 | 5  |

| AutoStore のディスエーブル化とイネーブル化 .....    | 5  |

| シリアル周辺デバイスインターフェイス .....            | 6  |

| SPI 概要 .....                        | 6  |

| SPI モード .....                       | 7  |

| SPI 動作特長 .....                      | 8  |

| パワーアップ .....                        | 8  |

| パワーダウン .....                        | 8  |

| アクティブ電力およびスタンバイ電力モード .....          | 8  |

| SPI 機能の説明 .....                     | 9  |

| 状態レジスタ .....                        | 10 |

| 読み取り状態レジスタ (RDSR) 命令 .....          | 10 |

| 高速読み取り状態レジスタ                        |    |

| (FAST_RDSR) 命令 .....                | 10 |

| 書き込み状態レジスタ (WRSR) 命令 .....          | 10 |

| 書き込み保護およびブロック保護 .....               | 11 |

| 書き込みイネーブル (WREN) 命令 .....           | 11 |

| 書き込みディスエーブル (WRDI) 命令 .....         | 12 |

| ブロック保護 .....                        | 12 |

| ハードウェア書き込み保護 (WP ピン) .....          | 12 |

| メモリアクセス .....                       | 12 |

| 読み取りシーケンス (READ) 命令 .....           | 12 |

| 高速読み取りシーケンス (FAST_READ) 命令 .....    | 12 |

| 書き込みシーケンス (WRITE) 命令 .....          | 13 |

| RTC アクセス .....                      | 15 |

| 読み取り RTC (RDRTC) 命令 .....           | 15 |

| 高速読み取りシーケンス                         |    |

| (FAST_READ) 命令 .....                | 15 |

| 書き込み RTC (WRTC) 命令 .....            | 16 |

| nvSRAM 特別命令 .....                   | 16 |

| ソフトウェア STORE(STORE) 命令 .....        | 16 |

| ソフトウェア RECALL(RECALL) 命令 .....      | 16 |

| AutoStore イネーブル (ASENB) 命令 .....    | 16 |

| AutoStore ディスエーブル (ASDISB) 命令 ..... | 17 |

| 特別命令 .....                          | 17 |

| SLEEP 命令 .....                      | 17 |

| シリアル番号 .....                        | 17 |

| WRSN (シリアル番号書き込み) 命令 .....          | 17 |

| RDSN (シリアル番号読み取り) 命令 .....          | 18 |

|                                     |    |

|-------------------------------------|----|

| FAST_RDSN                           |    |

| (高速シリアル番号読み取り) 命令 .....             | 18 |

| デバイス ID .....                       | 19 |

| RDID (デバイス ID 読み取り) 命令 .....        | 19 |

| FAST_RDID (高速デバイス ID 読み取り) 命令 ..... | 20 |

| HOLD ピン動作 .....                     | 20 |

| リアルタイムクロック動作 .....                  | 21 |

| nvTIME の動作 .....                    | 21 |

| クロックの動作 .....                       | 21 |

| クロックの読み取り .....                     | 21 |

| クロックの時間設定 .....                     | 21 |

| バックアップ電源 .....                      | 21 |

| 発振器の停止と開始 .....                     | 21 |

| クロックの校正 .....                       | 22 |

| アラーム .....                          | 22 |

| ウォッチドッグタイマ .....                    | 22 |

| プログラマブル方形波発生器 .....                 | 23 |

| 電源モニタ .....                         | 23 |

| バックアップ電源モニタ .....                   | 23 |

| 割り込み .....                          | 23 |

| 割り込みレジスタ .....                      | 23 |

| フラグレジスタ .....                       | 24 |

| 最大定格 .....                          | 30 |

| 動作範囲 .....                          | 30 |

| DC 電気的特性 .....                      | 30 |

| データ保持期間および書き換え回数 .....              | 31 |

| 容量 .....                            | 31 |

| 熱抵抗 .....                           | 32 |

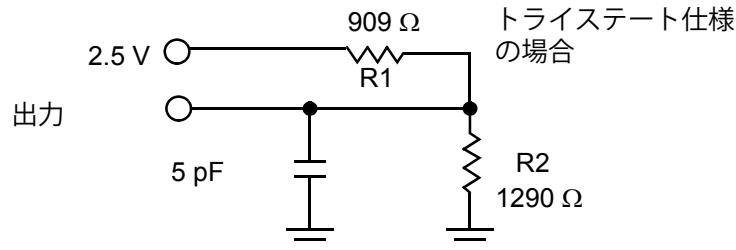

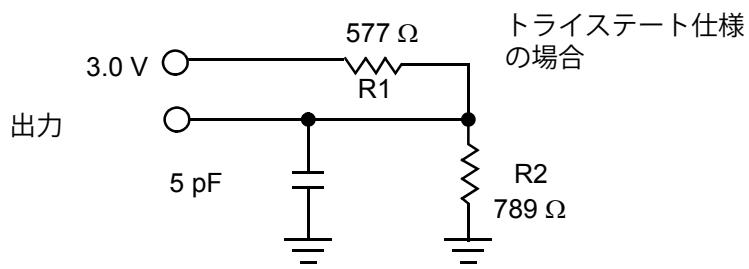

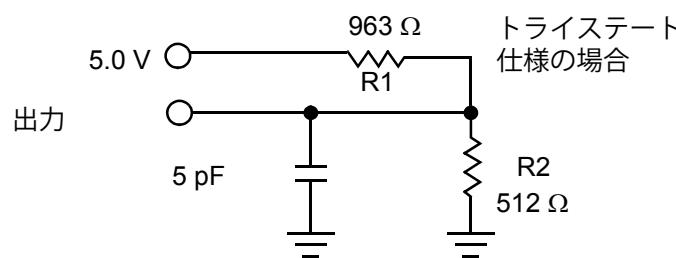

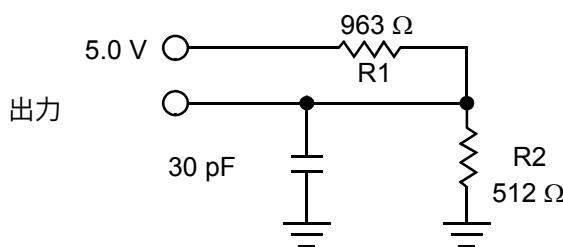

| AC テストの負荷および波形 .....                | 32 |

| AC テスト条件 .....                      | 32 |

| RTC 特性 .....                        | 33 |

| AC スイッチング特性 .....                   | 33 |

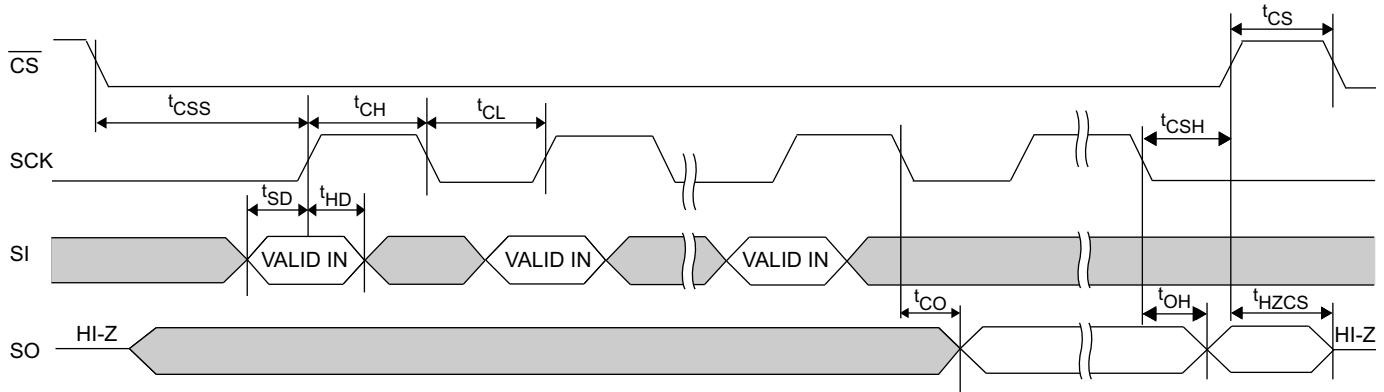

| スイッチング波形 .....                      | 34 |

| AutoStore またはパワーアップ RECALL .....    | 35 |

| スイッチング波形 .....                      | 35 |

| ソフトウェア制御 STORE/RECALL サイクル .....    | 36 |

| スイッチング波形 .....                      | 36 |

| ハードウェア STORE サイクル .....             | 37 |

| スイッチング波形 .....                      | 37 |

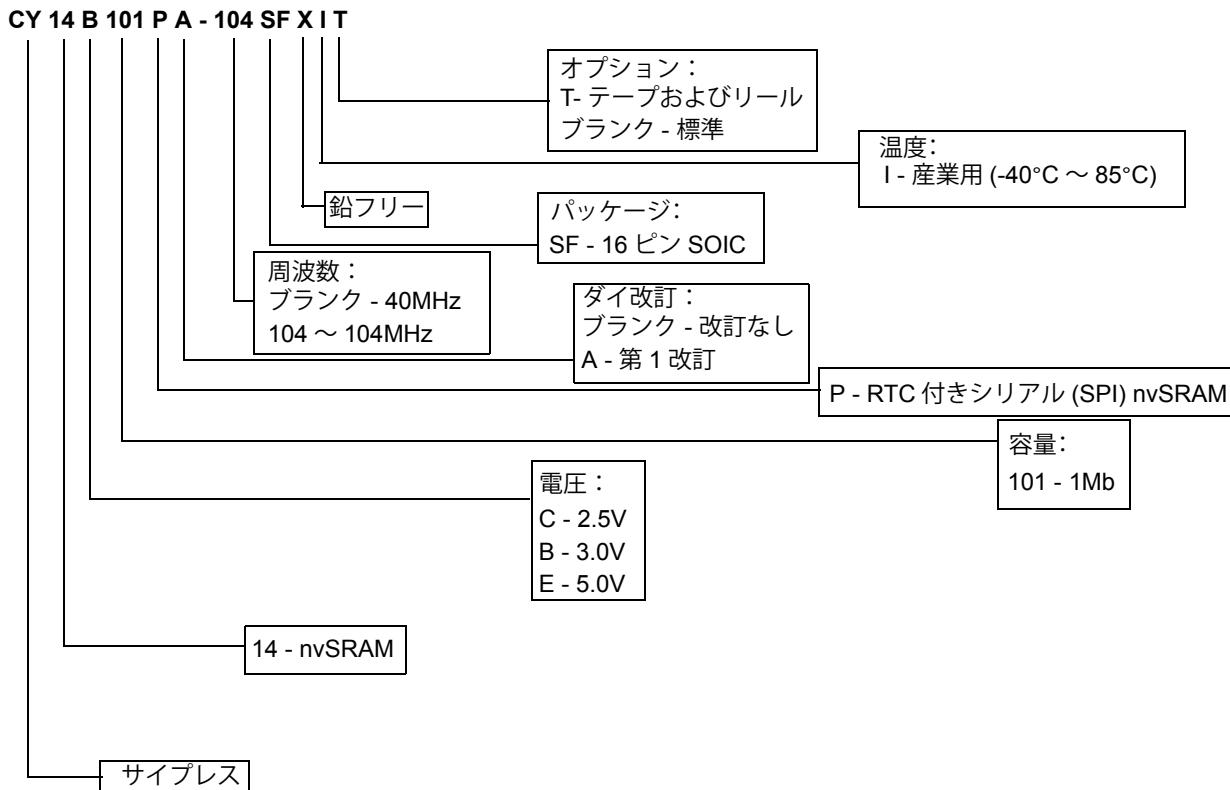

| 製品名(発注)情報 .....                     | 38 |

| 注文コードの定義 .....                      | 38 |

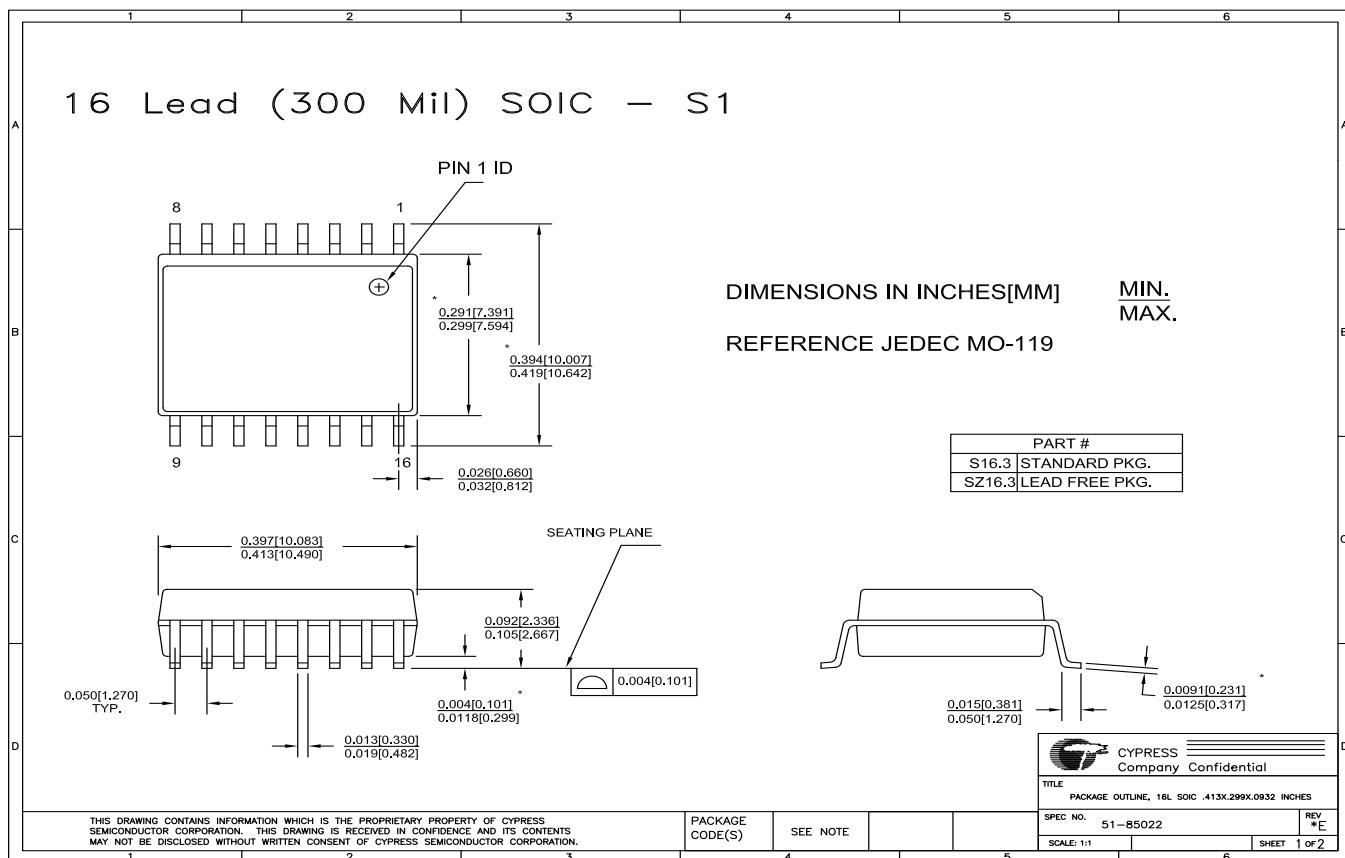

| パッケージ ダイヤグラム .....                  | 39 |

| 略号 .....                            | 40 |

| 本書の表記法 .....                        | 40 |

| 測定単位 .....                          | 40 |

| 改訂履歴 .....                          | 41 |

| 販売、ソリューション、および法律情報 .....            | 42 |

| ワールドワイドな販売および設計サポート .....           | 42 |

| 製品 .....                            | 42 |

| PSoC ソリューション .....                  | 42 |

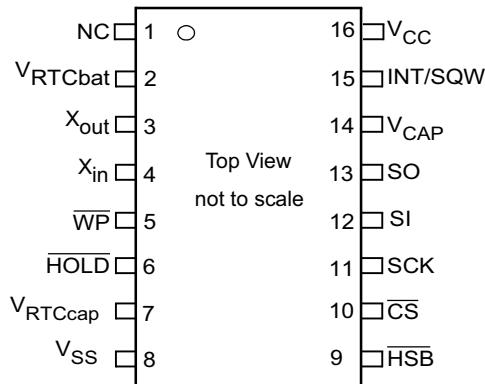

## ピン配列

図 1. 16 ピン SOIC ピン配列

## ピン機能

| ピン名              | 入出力  | 内容                                                                                                                                                                                                                                           |

|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{CS}$  | 入力   | チップセレクト：LOW にプルダウンされた時に、デバイスをアクティブ化します。このピンを HIGH に駆動すると、デバイスが低消費電力スタンバイモードになります。                                                                                                                                                            |

| SCK              | 入力   | シリアルクロック：最大 $f_{SCK}$ までの速度で動作します。シリアル入力はこのクロックの立ち上がりエッジでラッチされます。シリアル出力はクロックの立ち下がりエッジで駆動されます。                                                                                                                                                |

| SI               | 入力   | シリアル入力：すべての SPI 命令とデータの入力ピンです。                                                                                                                                                                                                               |

| SO               | 出力   | シリアル出力：SPI 経由のデータの出力ピンです。                                                                                                                                                                                                                    |

| WP               | 入力   | 書き込み保護：SPI にハードウェア書き込み保護を実装します。                                                                                                                                                                                                              |

| HOLD             | 入力   | HOLD ピン：シリアル動作をサスペンドします。                                                                                                                                                                                                                     |

| HSB              | 入出力  | ハードウェア STORE ビジー状態：<br>出力：LOW の時、nvSRAM のビジー状態を示します。ハードウェアおよびソフトウェア STORE オペレーションの後、HSB は HIGH 出力標準電流で短時間 ( $t_{HHD}$ ) HIGH 駆動され、その後内部プルアップ抵抗で HIGH 状態を継続します（外部プルアップ抵抗接続はオプションです）。<br>入力：ハードウェア STORE は、外部的にこのピンを LOW にプルダウンすることによって実装されます。 |

| $V_{CAP}$        | 電源   | AutoStore コンデンサ。SRAM から不揮発性要素にデータを格納するため、電力損失時に nvSRAM へ電源を供給します。AutoStore が必要でない場合は、このピンは接続不要として外しておきます。これは絶対にグランドに接続しないでください。                                                                                                              |

| $V_{RTCCap}$ [2] | 電源   | RTC のコンデンサバックアップ： $V_{RTCbat}$ が使用される場合は、未接続のままになります。                                                                                                                                                                                        |

| $V_{RTCbat}$ [2] | 電源   | RTC のバッテリバックアップ： $V_{RTCCap}$ が使用される場合は、未接続のままになります。                                                                                                                                                                                         |

| Xout [2]         | 出力   | 水晶出力接続                                                                                                                                                                                                                                       |

| Xin [2]          | 入力   | 水晶入力接続                                                                                                                                                                                                                                       |

| INT/SQW [2]      | 出力   | 割り込み出力 / 校正 / 方形波 クロックアラーム、ウォッチドッグタイマ、および電力モニタに対応するようにプログラム可能です。アクティブ HIGH (プッシュまたはプル) または LOW (オープンドレイン) のいずれにもプログラム可能です。校正モードでは、512Hz 方形波が出力されます。方形波モードでは、ユーザーは連続出力として使用される 1Hz、512Hz、4,096Hz、または 32,768Hz の周波数を選択することができます。               |

| NC               | 接続なし | 未接続。このピンはダイに接続されません。                                                                                                                                                                                                                         |

| $V_{SS}$         | 電源   | グランド                                                                                                                                                                                                                                         |

| $V_{CC}$         | 電源   | 電源                                                                                                                                                                                                                                           |

注

2. RTC 機能を使用しない場合は未接続のままにします。

## デバイスオペレーション

CY14X101PA は、統合された RTC と SPI インターフェイスを備えた 1Mbit SPI nvSRAM メモリです。nvSRAM へのすべての読み取りと書き込みは、メモリへの書き込みを無制限に処理可能にする独自の SRAM に対して行われます。SRAM 内のデータは、不揮発性 QuantumTrap セルへパラレルでデータを転送する STORE 命令によって保護されます。小容量コンデンサ ( $V_{CAP}$ ) は、電源パワーダウン時に不揮発性セルに SRAM データを AutoStore するために使われ、電源遮断時のデータセキュリティを提供します。信頼性の高い SONOS 技術を用いた QuantumTrap 不揮発性要素により、nvSRAM は安全なデータストレージのための理想的な選択肢を提供します。

CY14X101PA では、1Mbit のメモリアレイが 128 K ワード × 8 ビットとして編成されます。メモリは、読み書きサイクルの遅延サイクル値ゼロで最大 40MHz の非常に高いクロック速度が可能な標準 SPI インターフェイスを通じてアクセスされます。この nvSRAM チップは、読み取りオペレーションの特別命令を使用して、104MHz の SPI アクセス速度をサポートしています。CY14X101PA は、SPI モード 0 および 3 (CPOL、CPHA=0、0 および 1、1) をサポートし、SPI スレーブとして動作します。デバイスはチップセレクト (CS) 端子が使用でき、シリアル入力端子 (SI)、シリアル出力端子 (SO)、シリアルクロック端子 (SCK) を通じてアクセスします。

CY14X101PA は、WR ピンおよび WRDI 命令によるハードウェアおよびソフトウェアの書き込み保護の機能を提供します。CY14X101PA はまた、状態レジスタ内で BP0 端子と BP1 端子を使用して、ブロック書き込み保護（アレイの 1/4、1/2、またはすべてを保護）のメカニズムを提供します。さらに HOLD 端子は、シリアルシーケンスをリセットせずにすべてのシリアル通信を一時停止するために使われます。

CY14X101PA は、メモリへのアクセスに標準 SPI オペコードを使用します。読み書き用の一般的な SPI 命令に加え、CY14X101PA は 4 つの nvSRAM の特定機能にアクセス可能な、独自の 4 つの命令を実現します。STORE、RECALL、AutoStore Disable (ASDISB)、AutoStore Enable (ASENB) を提供します。

シリアル EEPROM に対する nvSRAM の主な利点は、nvSRAM のすべての読み書きは遅延サイクルゼロの SPI バス速度で実行されることです。そのため、どのメモリアクセスの後でも待ち時間は不要です。STORE と RECALL オペレーションは制限された時間で完了し、その間すべてのメモリアクセスは禁止されます。STORE または RECALL オペレーションの実行中は、ハードウェア STORE のビジー (HSB) ピンにデバイスのビジー状態が表示され、状態レジスタの RDY ピットにも反映されます。

## SRAM 書き込み

nvSRAM へのすべての書き込みは SRAM 上で実施され、不揮発性メモリのどのような持続サイクルも使い切ることはできません。これにより、無限の書き込みオペレーションを実行することができます。書き込みサイクルは WRITE 命令を通じて実行されます。WRITE 命令は nvSRAM の SI 端子より発行され、WRITE オペコードと、3 バイトのアドレス、1 バイトのデータで構成されます。nvSRAM への書き込みは遅延サイクルゼロの SPI バス速度で行われます。

CY14X101PA は、SPI 経由で実行されるバーストモードの書き込みが使用可能です。これにより、新しい WRITE オペレーションを発行せずに、連続したアドレス上で書き込み処理を実行できます。バーストモードでメモリの最後のアドレスに到達した時、アドレスは 0x00000 にロールオーバーされ、デバイスは書き込みを継続します。

SPI 書き込みサイクル命令は、SPI プロトコル記述のメモリアクセスセクションに定義されています。

## SRAM 読み込み

読み取りサイクルは、SPI バス速度で実行されます。データは READ 命令が実行された後、遅延ゼロサイクルで読み取られます。READ 命令は、最大 40MHz のクロック速度まで使用することができます。READ 命令は nvSRAM の SI ピン経由で発行され、READ オペコードと 3 バイトのアドレスで構成されます。データは SO 端子で読み出されます。

40MHz (最大 104MHz) よりも速い速度には、FAST\_READ 命令が必要です。FAST\_READ 命令は nvSRAM の SI ピン経由で発行され、FAST\_READ オペコード、3 バイトのアドレス、および 1 つのダミーバイトで構成されます。データは SO 端子で読み出されます。

CY14X101PA は、SPI 経由で実行されるバーストモードの読み込みが使用可能です。これにより、新しい READ 命令を発行せずに、連続したアドレス上で読み込み処理を実行できます。バーストモード読み取りでメモリの最後のアドレスに到達した時、アドレスは 0x00000 にロールオーバーされ、デバイスは読み取りを継続します。

SPI 読み取りサイクル命令は、SPI プロトコル記述のメモリアクセスセクションに定義されています。

## STORE 動作

STORE オペレーションは、SRAM から不揮発性 QuantumTrap セルへデータを転送します。CY14X101PA は、次の 3 つの STORE オペレーションのいずれかを使用してデータを不揮発性セルへ STORE します。デバイスのパワーダウンによりアティベートされる AutoStore、STORE 命令によってアティベートされるソフトウェア STORE、HSB によってアティベートされるハードウェア STORE です。STORE サイクルの実行中、まず以前の不揮発性データの消去が実行され、次に不揮発性素子のプログラムが実行されます。STORE サイクルが開始されると、CY14X101PA への書き込みはそのサイクルが完了するまで禁止されます。

状態レジスタ内の HSB 信号または RDY ピットは、STORE またはソフトウェア RECALL サイクルが実行中かどうかを検出するため、システムによる監視が可能です。nvSRAM のビジー状態は、HSB が LOW の状態になっているか、または RDY ピットが「1」に設定されていることによって示されます。不要な不揮発性の STORE を避けるため、AutoStore およびハードウェア STORE オペレーションは、一番最後に STORE または RECALL サイクルが実行されてから少なくとも 1 回の書き込みオペレーションが行われるまでは無視されます。ただし、STORE サイクルが起動されたソフトウェアは、書き込みオペレーションが行われたかどうかに係わらず実行されます。

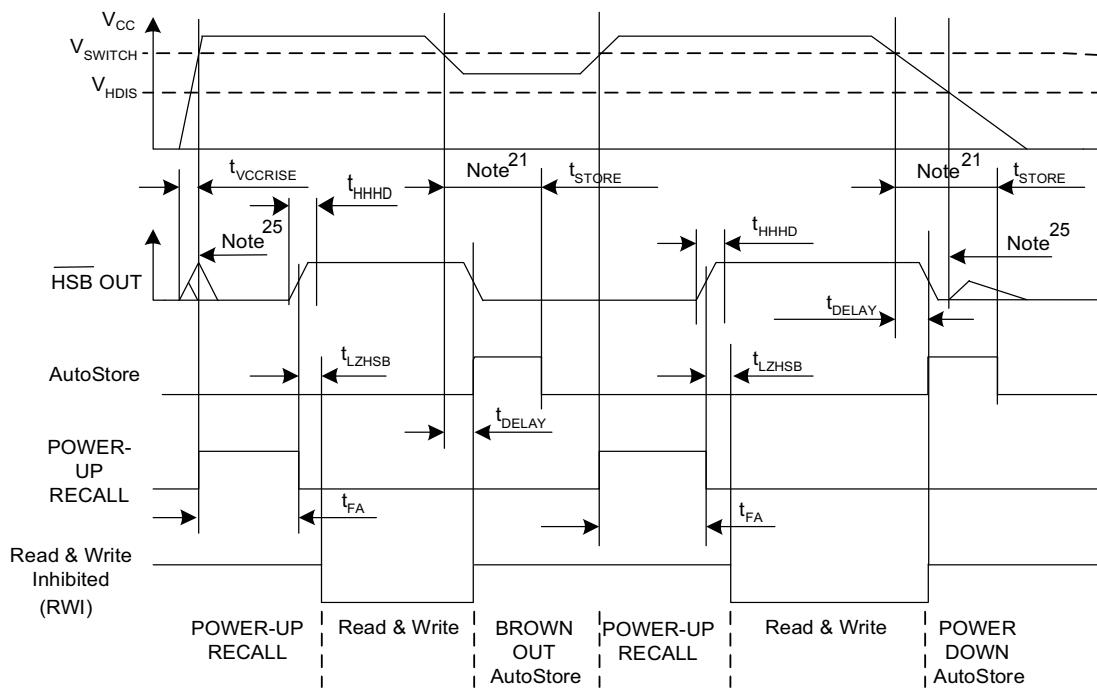

## AutoStore 処理

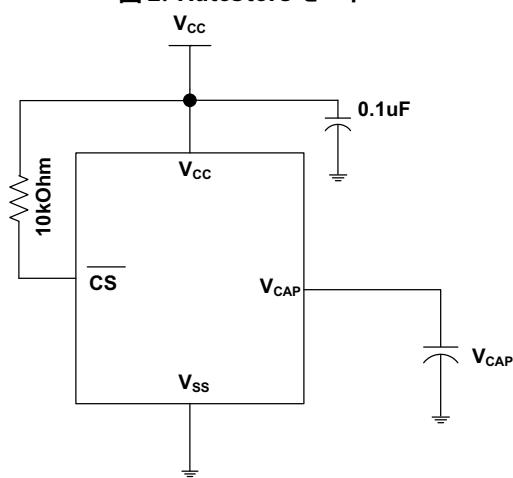

AutoStore オペレーションは、パワーダウン時に SRAM データを QuantumTrap セルに自動的に保存する、nvSRAM 独自の機能です。この STORE 処理では外付けコンデンサ ( $V_{CAP}$ ) を活用し、デバイスは電源遮断時に不揮発性メモリへ安全にデータを保存できるようにします。

通常オペレーション時、デバイスは  $V_{CC}$  から電流を得て、 $V_{CAP}$  ピンに接続されたコンデンサにチャージします。パワーダウン時に  $V_{CC}$  ピンの電圧が  $V_{SWITCH}$  以下に下がった場合、デバイスは nvSRAM へのメモリアクセスをすべて禁止し、 $V_{CAP}$  コンデンサからのチャージを使って自動的に条件付き STORE オペレーションを実行します。AutoStore オペレーションは、最後の RECALL の実行以降に書き込みサイクルが一度も実行されていない場合は起動されません。

**注** コンデンサが  $V_{CAP}$  ピンに接続されていない場合、AutoStore ディスエーブル命令を発行して AutoStore をディスエーブルに

する必要があります (17 ページの AutoStore ディスエーブル (ASDISB) 命令)。 $V_{CAP}$  ピンに接続されたコンデンサなしで AutoStore がアクティベートにされた場合、デバイスは STORE オペレーションを完了するため、十分なチャージがないまま AutoStore 動作を実行しようとします。これにより、nvSRAM に格納されているデータ、状態レジスタ、およびシリアル番号が破壊され、SNL ビットのロックが解除されます。通常の機能を再開するには、WRSR 命令を発行し、状態レジスタ内の不揮発性ビット BP0、BP1、WPEN を更新する必要があります。

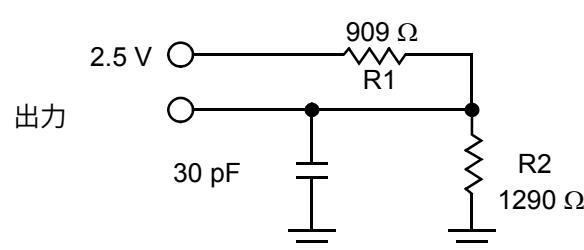

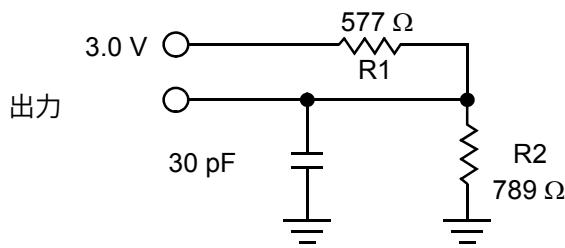

図 2 に、AutoStore オペレーション向けのストレージコンデンサ ( $V_{CAP}$ ) の適切な接続方法を示します。 $V_{CAP}$  の静電容量についてでは、30 ページの DC 電気的特性を参照してください。

図 2. AutoStore モード

### ソフトウェア STORE 動作

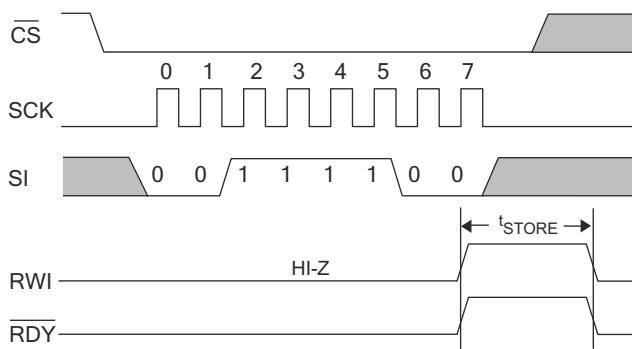

ソフトウェア STORE オペレーションでは、ユーザーは特定の SPI 命令を通じて STORE 处理をトリガーすることができます。STORE オペレーションは最後の NV オペレーション以降に書き込みが実行されたかどうかに関係なく、STORE 命令の実行によって開始します。

STORE サイクルが完了するまでに  $t_{STORE}$  の時間がかかりますが、その間 nvSRAM へのすべてのメモリアクセスは禁止されます。状態レジスタの RDY ビットまたは HSB ピンは、nvSRAM のレディ / ビジー状態を検出するためにポーリングされる可能性があります。 $t_{STORE}$  サイクル時間が完了した後、SRAM は再度読み書きオペレーションがアクティベートされます。

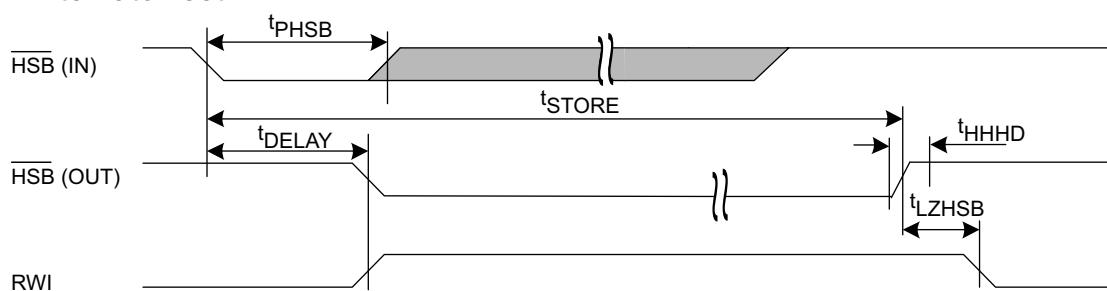

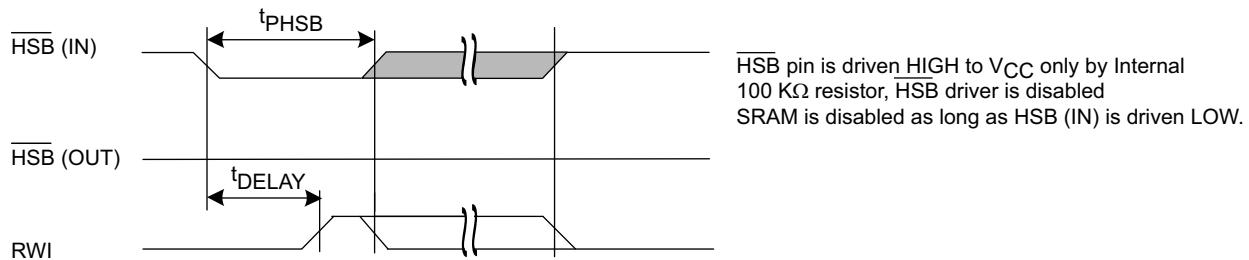

### ハードウェア STORE 動作および HSB ピン動作

CY14X101PA 内の HSB 端子は、STORE オペレーションを制御し応答するために使用されます。実行中の STORE/RECALL 処理が存在しなければ、この端子はハードウェアによる STORE サイクルをリクエストするために使用できます。HSB ピンが LOW で駆動された場合、CY14X101PA は  $t_{DELAY}$  の継続後、条件付きで STORE オペレーションを開始します。STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始されます。 $t_{STORE}$  が継続中か HSB ピンが LOW である限り、メモリへの読み書きは禁止されます。HSB ピンは、チップ内部で 100 kΩ のプルアップ抵抗を持つオープンドレイン出力でもあります。開始イベントを問わず、STORE 動作中にはビジー状態を意味する LOW レベルを出力します。

注 ハードウェアおよびソフトウェア STORE オペレーションの後、HSB は HIGH 出力標準電流で短時間 ( $t_{HHHD}$ ) HIGH 駆動さ

れ、その後 100 kΩ の内部プルアップ抵抗により HIGH 状態を継続します。

注 最後のデータバイトのストアを正常に実行するため、ハードウェアストアでは最後のデータビット D0 が受信された後、最低 1 クロックサイクルを開始するべきです。

STORE オペレーションが完了すると、HSB ピンが HIGH を返した後、nvSRAM メモリアクセスは  $t_{LZHSB}$  時間の間禁止されます。HSB 端子は、未使用の場合は接続していない状態である必要があります。

### RECALL 处理

RECALL オペレーションは、QuantumTrap 不揮発性要素内にストアされたデータを SRAM へ転送します。CY14X101PA では、RECALL は 2 つの方法でイニシエート：ハードウェア RECALL (パワーアップで開始) およびソフトウェア RECALL (SPI RECALL 命令によって開始) の 2 つです。

内部的に、RECALL は 2 段階の手順を踏みます。まず SRAM データがクリアされ、次に不揮発性情報が SRAM セルに転送されます。RECALL サイクルの実行中、メモリアクセスはすべて禁止されます。RECALL オペレーションでは不揮発性素子内のデータは変更されません。

### ハードウェア RECALL (電源オン)

パワーアップの間に  $V_{CC}$  が  $V_{SWITCH}$  を超えると、SRAM 上に不揮発性メモリの内容を転送する RECALL シーケンスが自動的に開始されます。データはそれ以前に STORE シーケンスを通じて不揮発性メモリに格納されることになっています。

電源オン RECALL サイクルが完了するまでには  $t_{FA}$  の時間がかかり、その間のメモリアクセスはディスエーブルとなります。HSB ピンはデバイスのレディ状態を検出するために使われます。

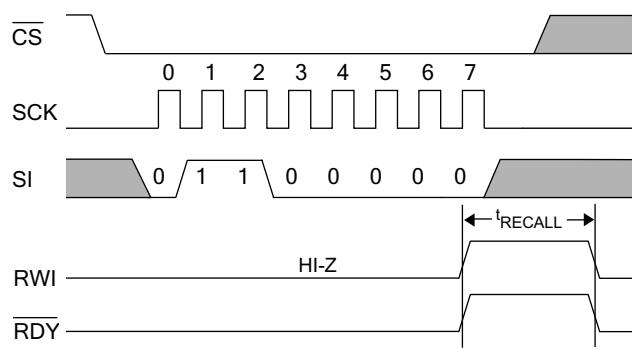

### ソフトウェア RECALL

ソフトウェアオペレーションにより、ユーザーは RECALL 動作を実行し、SRAM で不揮発性メモリの内容を復元できます。では、CY14X101PASPI で RECALL 命令を発行することによってこれを実行できます。

ソフトウェア RECALL が完了するまでには  $t_{RECALL}$  の時間がかかり、その間 nvSRAM へのすべてのメモリアクセスは禁止されます。コントローラは、すべてのメモリアクセス命令の発行前に RECALL オペレーションを完了するよう、十分な遅延を提供する必要があります。

### AutoStore のディスエーブル化とイネーブル化

AutoStore 機能の適用が不要な場合、ASDISB 命令により CY14X101PA でディスエーブル化できます。これを実行すると、nvSRAM はパワーダウン時に STORE オペレーションを実行しません。

AutoStore は ASENB 命令を使って再度イネーブルにできます。しかし、これらのオペレーションは不揮発性ではないため、パワーサイクルを存続するためにこの設定を必要とする場合、AutoStore のディスエーブル化とイネーブル化オペレーションの後に必ず STORE オペレーションを実行しなければなりません。

注 CY14X101PA 工場出荷時、の AutoStore はイネーブルになっています。

注 AutoStore がディスエーブルかつ  $V_{CAP}$  が不要の場合、 $V_{CAP}$  ピンは開回路のままにしておく必要があります。 $V_{CAP}$  端子は絶対にグランドに接続しないでください。パワーアップ RECALL オペレーションは、どのような場合でもディスエーブルにできません。

## Serial Peripheral Interface (シリアル周辺デバイスインターフェース)

### SPI 概要

SPI は、チップセレクト ( $\overline{CS}$ )、シリアル入力 (SI)、シリアル出力 (SO)、およびシリアルクロック (SCK) ピンの 4 ピンインターフェイスです。CY14X101PA は、SPI インターフェイス経由で nvSRAM にシリアルアクセスを提供します。RDRTC および READ 命令を除き、CY14X101PA の SPI バスは最大 104MHz の速度で実行することができます。

SPI は、メモリアクセスにクロックとデータピンを使用し、データバス上の複数デバイスをサポートする同期シリアルインターフェイスです。SPI バスデバイスは、CS ピンを使用してアクティブ化されます。

チップセレクト、クロック、データの間の関係は、SPI モードによって左右されます。CY14X101PA は SPI モード 0 および 3 をサポートしています。これらの両モードで、 $\overline{CS}$  がアクティブ化された後の最初の立ち上がりエッジから始まる SCK の立ち上がりエッジでデータが nvSRAM にクロック入力されます。

SPI プロトコルはオペコードによって制御されます。これらのオペコードは、バスマスタからスレーブデバイスへのコマンドを指定します。 $\overline{CS}$  がアクティブ化された後、バスマスタから転送される最初のバイトがオペコードです。オペコードに続いて、アドレスとデータが転送されます。動作完了後、新しいオペコードが発行される前に、CS が非アクティブ化される必要があります。

SPI プロトコルで使用される一般的用語は以下の通りです。

### SPI マスタ

SPI マスタデバイスは、SPI バス上のオペレーションを制御します。SPI バスは、1 つまたは複数のスレーブデバイスを持つ 1 つのマスタを持っている場合があります。すべてのスレーブが同じ SPI バスラインを共有し、マスタは  $\overline{CS}$  ピンを使用してスレーブデバイスのいずれかを選択することができます。すべてのオペレーションは、マスタがスレーブの CS ピンを LOW にプルダウンすることによってスレーブデバイスをアクティブ化して開始される必要があります。マスタはまた SCK も生成し、SI および SO ラインのすべてのデータ送信はこのクロックに同期されます。

### SPI スレーブ

SPI スレーブデバイスは、チップセレクトラインを介してマスタによってアクティブ化されます。スレーブデバイスは、SPI マスタからの入力として SCK を取得し、すべての通信はこのクロックに同期されます。SPI スレーブが SPI バスでの通信を開始することではなく、これはマスタからの命令に従って動きます。CY14X101PA はスレーブデバイスとして動作し、複数の CY14X101PA デバイスまたは他の SPI デバイスと SPI バスを共有する場合があります。

### チップセレクト ( $\overline{CS}$ )

すべてのスレーブデバイスを選択するために、マスタは対応する  $\overline{CS}$  ピンをプルダウンする必要があります。 $\overline{CS}$  ピンが LOW の間だけ、命令をスレーブデバイスに発行することができます。

$\overline{CS}$  ピンが LOW の時、CY14X101PA が選択されます。デバイスが選択されていない場合、SI ピン経由のデータは無視され、シリアル出力ピン (SO) はハイインピーダンス状態のままでなります。

注 新しい命令は  $\overline{CS}$  の立ち下がりエッジで開始される必要があります。したがって、アクティブな各チップセレクトサイクルに対して 1 つのオペコードのみが発行されます。

### シリアルクロック (SCK)

シリアルクロックは SPI マスタによって生成され、 $\overline{CS}$  が LOW になった後、通信がこのクロックに同期されます。

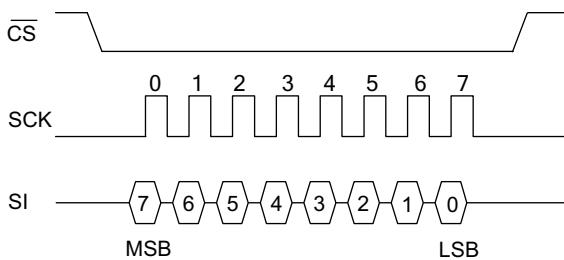

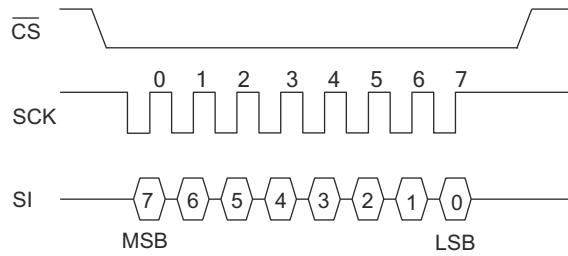

CY14X101PA はデータ通信のために SPI モード 0 と 3 を可能にします。これらの両モードにおいて、入力は SCK の立ち上がりエッジでスレーブデバイスによってラッチされ、出力は立ち下がりエッジで発行されます。そのため、SCK の最初の立ち上がりエッジが SI ピンにおける SPI 命令の最初のビット (MSB) 到着を意味します。さらに、すべてのデータの入力と出力は SCK に同期されます。

### データ送信 SI/SO

SPI データバスは、シリアルデータ通信用に SI と SO の 2 ラインで構成されます。SI はマスタアウトスレーブイン (MOSI)、SO はマスタインスレーブアウト (MISO) と呼ばれています。マスタは SI ピンを介してスレーブに命令を発し、スレーブは SO ピンを介して応答します。複数のスレーブデバイスは、前述のように SI と SO ラインを共有する場合があります。

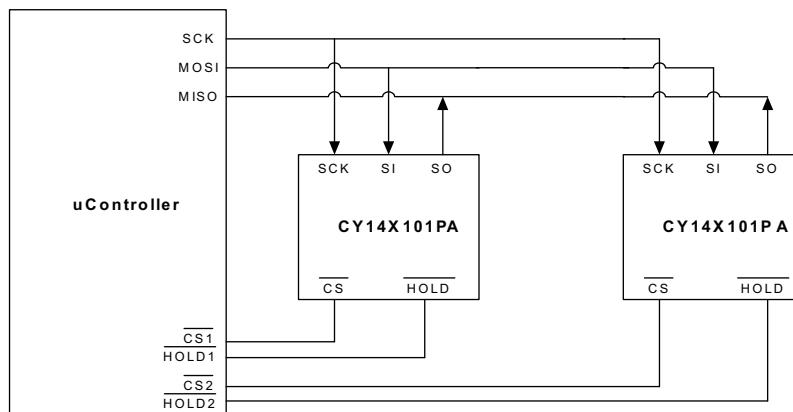

CY14X101PA には、7 ページの図 3 に示されているように、SI と SO 用にマスタと接続することができる 2 つの独立したピンがあります。

### 最上位ビット (MSB)

SPI プロトコルでは、送信される最初のビットが最上位ビット (MSB) であることが必要です。これは、アドレスとデータ送信の両方に有効です。

CY14X101PA は、すべての読み取りまたは書き込みオペレーションにおいて 3 バイトのアドレスを必要とします。しかし、アドレスは 17 ビットであるため、入力された最初の 7 ビットはデバイスによって無視されることを意味します。これらの 7 ビットは「ドント・ケア」ですが、より高いメモリ密度へのシームレスな移行を可能にするために、これらを 0 として扱うことをサイプレスはお勧めしています。

### シリアルオペレーションコード

$\overline{CS}$  が LOW になる状態でスレーブデバイスが選択された後、最初に受信されたバイトは、意図されているオペレーションのオペコードとして扱われます。

CY14X101PA は、メモリアクセスに標準オペコードを使用します。メモリアクセスに加えて、CY14X101PA は nvSRAM の特定機能のために追加のオペコードを提供します。STORE、RECALL、AutoStore イネーブル、および AutoStore ディスエーブルです。オペコードの詳細については、9 ページの表 1 を参照してください。

### 無効なオペレーションコード

無効なオペコードが受信されると、そのオペコードは無視され、次の  $\overline{CS}$  の立ち下がりエッジまでデバイスは SI ピン上の追加のシリアルデータを無視し、SO ピンはトライステートのままとなります。

### 状態レジスタ

CY14X101PA には 8 ビットの状態レジスタがあります。状態レジスタ内のビットは、SPI バスを構成するために使用されます。これらのビットは 10 ページの表 3 に説明されています。

**図 3. SPI nvSRAM を用いたシステム構成**

## SPI モード

CY14X101PA は、その SPI 周辺回路がこれら 2 つのモードのいずれかで実行されているマイクロコントローラによって駆動することができます。

■ SPI モード 0 (CPOL=0, CPHA=0)

■ SPI モード 3 (CPOL=1, CPHA=1)

これらの両モードで、CS がアクティビ化された後の最初の立ち上がりエッジから始まる SCK の立ち上がりエッジで入力データがラッチされます。クロックが HIGH 状態（モード 3）から起動する場合は、クロックのトグル後の最初の立ち上がりエッジが考えられます。出力データは SCK の立ち下がりエッジで利用可能となります。

2 つの SPI モードは図 4 と図 5 に示されています。バスマスターがスタンバイモードで、データを転送していないクロックの状態は以下の通りです。

■ SCK はモード 0 で 0 のままで。

■ SCK はモード 3 で 1 のままで。

CPOL と CPHA ビットは、SPI コントローラでモード 0 かモード 3 のいずれかに設定される必要があります。CS ピンを LOW にすることによってデバイスが選択された時、CY14X101PA は SCK ピンの状態から SPI モードを検出します。デバイスが選択された時に SCK ピンが LOW の場合は SPI モード 0 が想定され、SCK ピンが HIGH の場合は CY14X101PA は SPI モード 3 で動作します。

**図 4. SPI モード 0**

**図 5. SPI モード 3**

## SPI 動作特長

### パワーアップ

パワーアップは、電源がオンになっていて、 $V_{CCV}$  が  $V_{switch}$  電圧を超えた状態として定義されます。

前述のように、パワーアップ nvSRAM は、すべてのメモリアクセスがディスエーブルになっている間に、 $t_{FA}$  の持続のためにパワーアップ RECALL オペレーションを実行します。パワーアップ後、nvSRAM のレディ / ビジー状態をチェックするために、HSB ピンをプローブすることができます。

以下はパワーアップ後のデバイス状態です。

- $\overline{CS}$  ピンが LOW の場合、選択 (アクティブパワーモード)

- $\overline{CS}$  ピンが HIGH の場合、選択解除 (スタンバイパワーモード)

- ホールド中でない状態

- 状態レジスタの状態：

- 書き込みイネーブル (WEN) ビットが「0」にリセット。

- WPEN、BP1、BP0 は前回の STORE オペレーションから変化しません。

- 状態レジスタの WPEN、BP1、および BP0 ビットは不揮発性ビットであり、前回の STORE オペレーションから変更されないままとなります。

### パワーダウン

パワーダウン時 ( $V_{CC}$  の連続減衰)、 $V_{CC}$  が通常の動作電圧を下回り、 $V_{SWITCH}$  の閾値電圧より下になると、デバイスはそれに送られたすべての命令への応答を停止します。書き込みサイクルが進行中であり、電源がダウンした時に最後のデータビット D0 が受信された場合は、書き込みを完了させるまでの  $t_{DELAY}$  時間が許可されています。この後は、すべてのメモリアクセスが禁止され、条件付き AutoStore オペレーションが実行されます (最後の RECALL サイクル以降に書き込みが行われていない場合は、AutoStore が実行されます)。この機能により、パワーダウン時に不注意な nvSRAM への書き込みが行われるのを防ぐことができます。しかし、パワーダウン時の不注意な書き込みの可能性を防止するために、デバイスが選択解除されていること、およびスタンバイパワーモードになっていることを確認する必要があります。そうすれば、 $\overline{CS}$  は  $V_{CC}$  に印加される電圧に従います。

### アクティブ電力およびスタンバイ電力モード

$\overline{CS}$  が LOW の時、デバイスが選択され、アクティブパワーモードになります。[30 ページの DC 電気的特性](#)で指定されているように、デバイスは  $I_{CC}$  電流を消費します。 $\overline{CS}$  が HIGH の時、デバイスは選択解除され、STORE または RECALL サイクルが進行中でなければ、デバイスは  $t_{SB}$  時間後にスタンバイパワーモードとなります。STORE/RECALL サイクルが進行中の場合、STORE/RECALL サイクルが完了した後に、デバイスがスタンバイパワーモードになります。スタンバイパワーモードでは、デバイスに流れる電流は  $I_{SB}$  に低下します。

## SPI 機能の説明

CY14X101PA は 8 ビット命令レジスタを使用します。命令とそのオペレーションコードは表 1 に一覧されています。すべての命令、アドレス、データは、最初に MSB とともに転送され、HIGH から LOW CSへの遷移で開始されます。nvSRAM でほとんどの機能へのアクセスを提供する全部で 21 の SPI 命令があります。さらに、WP、HOLD、および HSB ピンがハードウェアを介して駆動される追加機能を提供します。

表 1. 命令セット

| 命令カテゴリ                    | 命令名        | オペレーションコード | 動作                                               |

|---------------------------|------------|------------|--------------------------------------------------|

| <b>状態レジスタ制御命令</b>         |            |            |                                                  |

| 状態レジスタアクセス                | RDSR       | 0000 0101  | 読み取り状態レジスタ                                       |

|                           | FAST_RDSR  | 0000 1001  | 高速状態レジスタ読み取り - SPI クロック > 40MHz                  |

|                           | WRSR       | 0000 0001  | 書き込み状態レジスタ                                       |

| 書き込み保護および<br>ブロック保護       | WREN       | 0000 0110  | 書き込みイネーブルラッチを設定                                  |

|                           | WRDI       | 0000 0100  | 書き込みイネーブルラッチをリセット                                |

| <b>SRAM 読み取り / 書き込み命令</b> |            |            |                                                  |

| メモリアクセス                   | 読み取り       | 0000 0011  | メモリアレイからの読み取りデータ                                 |

|                           | FAST_READ  | 0000 1011  | 高速読み取り - SPI クロック > 40MHz                        |

|                           | 書き込み       | 0000 0010  | メモリアレイへの書き込みデータ                                  |

| <b>RTC 読み取り / 書き込み命令</b>  |            |            |                                                  |

| RTC アクセス                  | RDRTC      | 0001 0011  | 読み取り RTC レジスタ                                    |

|                           | FAST_RDRTC | 0001 1101  | 高速 RTC レジスタ読み取り - SPI クロック > 25MHz               |

|                           | WRTC       | 0001 0010  | 書き込み RTC レジスタ                                    |

| <b>特別 NV 命令</b>           |            |            |                                                  |

| nvSRAM 特別命令               | STORE      | 0011 1100  | ソフトウェア STORE                                     |

|                           | RECALL     | 0110 0000  | ソフトウェア RECALL                                    |

|                           | ASENB      | 0101 1001  | AutoStore イネーブル                                  |

|                           | ASDISB     | 0001 1001  | AutoStore ディスエーブル                                |

| <b>特別命令</b>               |            |            |                                                  |

| シリアル番号                    | SLEEP      | 1011 1001  | スリープモードイネーブル                                     |

|                           | WRSN       | 1100 0010  | 書き込みシリアル番号                                       |

|                           | RDSN       | 1100 0011  | 読み取りシリアル番号                                       |

|                           | FAST_RDSN  | 1100 1001  | 高速読み取りシリアル番号 - SPI クロック > 40MHz                  |

| デバイス ID 読み取り              | RDID       | 1001 1111  | メーカー JEDEC ID および製品 ID 読み取り                      |

|                           | FAST_RDID  | 1001 1001  | 高速メーカー JEDEC ID および製品 ID 読み取り - SPI クロック > 40MHz |

| 予約済み                      | - 予約済み -   | 0001 1110  |                                                  |

CY14X101PA の SPI 命令はその機能に基づいてこれらのタイプに分類されます。

■ 状態レジスタ制御命令 :

- 状態レジスタアクセス : RDSR、FAST\_RDSR、および WRSR 命令

- 書き込み保護およびブロック保護: WP ピンと WEN、BP0、BP1 ビットの他に WREN および WRDI 命令

■ SRAM 読み取り / 書き込み命令

- メモリアクセス: READ、FAST\_READ、および WRITE 命令

■ RTC 読み取り / 書き込み命令

- RTC アクセス: RDRTC、FAST\_RDRTC、および WRTC 命令

■ 特別 NV 命令

- nvSRAM 特別命令 : STORE、RECALL、ASENB、および ASDISB

■ 特別命令 : SLEEP、WRSN、RDSN、FAST\_RDSN、RDID、FAST\_RDID

## 状態レジスタ

状態レジスタのビットは表2に一覧されています。状態レジスタは、レディビット(RDY)およびデータ保護ビットBP1、BP0、WEN、WPENで構成されます。nvSRAM STOREまたはソフトウェア RECALLサイクルが進行中、レディ/ビジー状態を確認するために、RDYビットをポーリングすることができます。状態レジスタは WRSR命令によって変更でき、RDSRまたはFAST\_RDSR命令で読み取ることができます。しかし、WRSR命令を使用して変更できるのは、状態レジスタのWPEN、BP1、およびBP0ビットのみです。WRSR命令は WENと RDYビットに影響を与えません。WEN、BP0、BP1、ビット4-5、SNL、およびWPENの工場出荷時のデフォルト値は「0」です。

状態レジスタの SNL(ビット6)は、WRSR命令を使用して書かれたシリアル番号をロックするために使用されます。そのビットが「0」の間は、シリアル番号はWRSR命令を使用して複数書き込むことができます。「1」に設定されている場合、このビットはシリアル番号に変更が加えられるのを防止します。このビットは工場で「0」にプログラムされており、一度だけ書き込むことができます。このビットが「1」に設定された後は、「0」にクリアすることはできません。

表2. 状態レジスタフォーマット

| ビット7     | ビット6    | ビット5  | ビット4  | ビット3    | ビット2    | ビット1    | ビット0 |

|----------|---------|-------|-------|---------|---------|---------|------|

| WPEN (0) | SNL (0) | X (0) | X (0) | BP1 (0) | BP1 (0) | WEN (0) | RDY  |

表3. 状態レジスタのビット定義

| ビット            | 定義             | 内容                                                                                                          |

|----------------|----------------|-------------------------------------------------------------------------------------------------------------|

| ビット0<br>(RDY)  | Ready (準備完了)   | 読み取り専用ビットは、デバイスがメモリアクセスの実行に対してレディ状態であること表示しています。STOREまたはソフトウェア RECALLサイクルの進行中、このビットはデバイスによって「1」に設定されます。     |

| ビット1<br>(WEN)  | 書き込みイネーブル      | WENはデバイスの書き込みがイネーブルかどうかを示します。パワーアップ時のこのビットのデフォルトは、0(ディスエーブル)です。<br>WEN=「1」→書き込みイネーブル<br>WEN=「0」→書き込みディスエーブル |

| ビット2<br>(BP0)  | ブロック保護ビット「0」   | ブロック保護のために使用されます。詳細については、 <a href="#">12ページの表4</a> をご覧ください。                                                 |

| ビット3<br>(BP1)  | ブロック保護ビット「1」   | ブロック保護のために使用されます。詳細については、 <a href="#">12ページの表4</a> をご覧ください。                                                 |

| ビット4-5         | ドント・ケア         | これらのビットは書き込み不可であり、常に読み取り時に「0」を返します。                                                                         |

| ビット6<br>(SNL)  | シリアル番号ロック      | 「1」に設定されてシリアル番号をロックします。                                                                                     |

| ビット7<br>(WPEN) | 書き込み保護イネーブルビット | 書き込み保護ピンの機能をイネーブルにするために使用されます(WP)。詳細については、 <a href="#">12ページの表5</a> をご覧ください。                                |

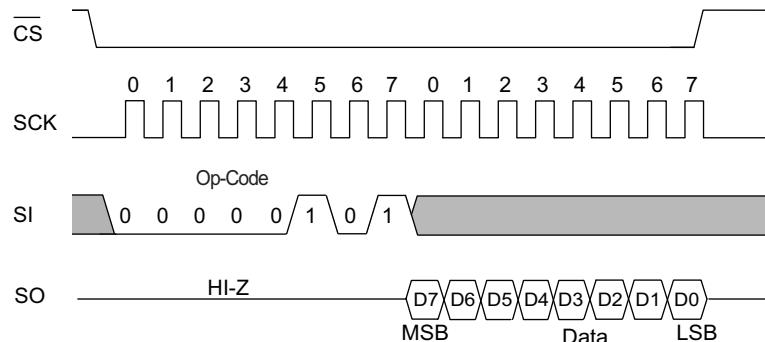

### 読み取り状態レジスタ (RDSR) 命令

読み取り状態レジスタ命令は、SPI周波数最大40MHzで状態レジスタへのアクセスを提供します。この命令は、デバイスの状態やデバイスのレディ状態を書き込みイネーブルにプローブするために使用されます。STOREまたはソフトウェア RECALLサイクルの進行中は常に、RDYビットはデバイスによって「1」に設定されます。ブロック保護とWPENビットは、用いられる保護の範囲を示します。

この命令は、RDSRのオペコードを使用して、CSの立ち下がりエッジの後に発行されます。

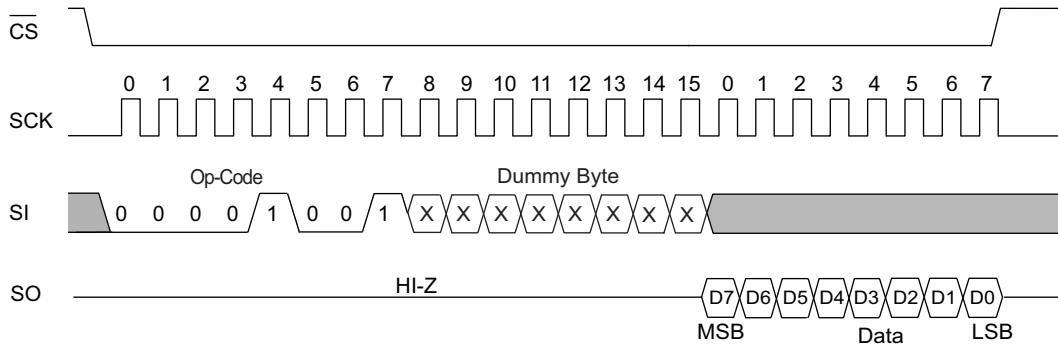

### 高速読み取り状態レジスタ (FAST\_RDSR) 命令

FAST\_RDSR命令により、SPI周波数40MHz以上、最大104MHz(最大)まで、状態レジスタを読み取ることができます。この命令は、デバイスの状態やデバイスのレディ状態を書き込みイネーブルにプローブするために使用されます。STOREまたはソフトウェア RECALLサイクルの進行中は常に、RDYビットはデバイスによって「1」に設定されます。ブロック保護とWPENビットは、用いられる保護の範囲を示します。

この命令は、RDSRのオペコードを使用して、ダミーバイトが後に続くCSの立ち下がりエッジの後に発行されます。

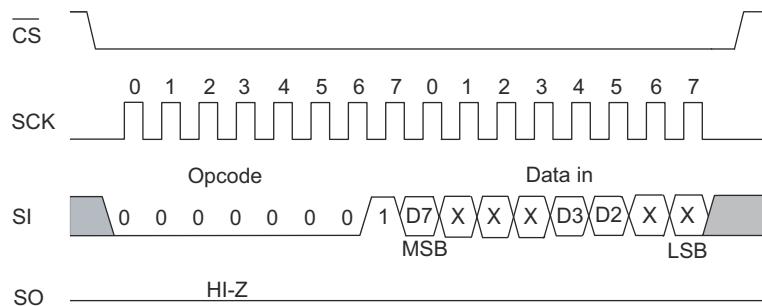

### 書き込み状態レジスタ (WRSR) 命令

WRSR命令により、ユーザーによる状態レジスタへの書き込みを可能にします。しかし、この命令はビット0(RDY)、ビット1(WEN)、およびビット4-5を変更するために使用することはできません。BP0とBP1ビットは、ブロック保護の4つのレベルのいずれかを選択するために使用できます。さらに、書き込み保護(WP)ピンの使用をイネーブルにするには、WPENビットは「1」に設定されている必要があります。

WRSR命令は書き込み命令であり、それが発行される前に、WREN命令を使用して(WENビットは「1」に設定)書き込みがイネーブルにされている必要があります。WRSRのオペコードを使用したCSの立ち下がりエッジの後に命令が発行され、その後に状態レジスタに格納される8ビットのデータが続きます。WRSR命令は、状態レジスタのビット2、3、6、および7のみを変更するために使用できます。

注 CY14X101PAでは、状態レジスタに書き込まれた値は、STOREオペレーションの後にのみ不揮発性メモリに保存されます。AutoStoreがディスエーブルになっている場合は、状態レジスタに加えられた変更は、ソフトウェア STOREオペレーションを実行して確保する必要があります。

**図 6. 読み取り状態レジスタ (RDSR) 命令タイミング**

**図 7. 高速読み取り状態レジスタ (FAST\_RDSR) 命令タイミング**

**図 8. 書き込み状態レジスタ (WRSR) 命令タイミング**

## 書き込み保護およびブロック保護

CY14X101PA は、WRDI 命令と WP を使用して、ソフトウェアとハードウェア書き込み保護の両方に機能を提供します。加えてこのデバイスは、状態レジスタの BP0 および BP1 ピンを介して、ブロック保護メカニズムを提供します。

デバイスの書き込みイネーブル / ディスエーブル状態は、状態レジスタの WEN ビットによって示されます。書き込み命令 (WRSR、WRITE、WRTC、および WRSN) および nvSRAM 特別命令 (STORE、RECALL、ASENB、ASDISB) は、これらが発行される前に書き込みがイネーブル (WEN ビット = '1') になっている必要があります。

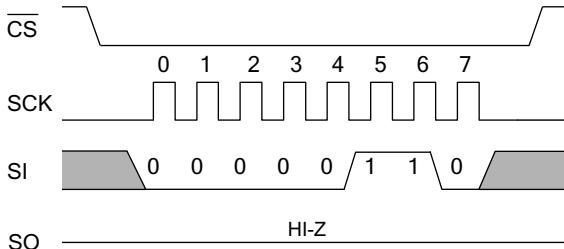

## 書き込みイネーブル (WREN) 命令

パワーアップ時、デバイスは常に書き込みディスエーブル状態にあります。したがって、以下の WRITE、WRSR、WRSN、または nvSRAM 特別命令の前に、書き込みイネーブル命令が発行されている必要があります。デバイスが書き込みイネーブル (WEN = '0') になっていない場合は、それは書き込み命令を無視し、CS が HIGH になるとスタンバイ状態に戻ります。シリアル通信を再開させるには、新しい CS の立ち下がりエッジが必要です。命令は CS の立ち下がりエッジ後に発行されます。この命令が使用される時、状態レジスタの WEN ビットは '1' に設定されています。パワーアップ時の WEN ビットのデフォルトは '0' です。

**注** 書き込み命令 (WRSR、WRITE、WRTC、または WRSN) または nvSRAM 特別命令 (STORE、RECALL、ASENB、ASDISB) の完了後、WEN ビットは '0' にクリアされます。これにより、不注意な書き込みが防止されます。したがって、WREN 命令は新しい書き込み命令が発行される前に使用される必要があります。

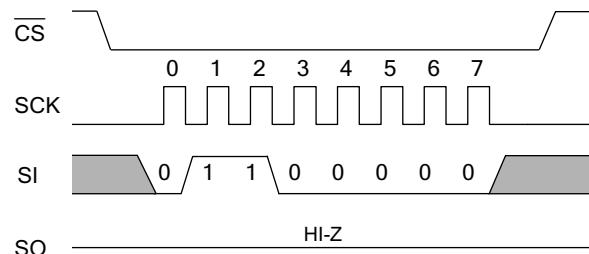

**図 9. WREN 命令**

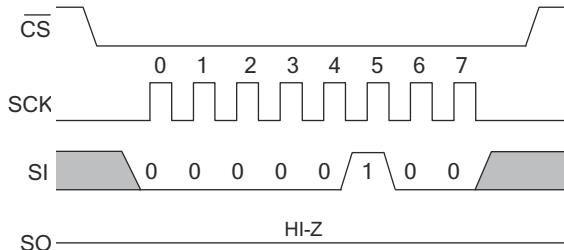

### 書き込みディスエーブル (WRDI) 命令

不注意な書き込みからデバイスを保護するために、書き込みディスエーブル命令により WEN ビットが「0」にクリアされ、書き込みがディスエーブルとなります。この命令は CS の立ち下がりエッジ後に発行され、その後に WRDI 命令のオペコードが続きます。WEN ビットは WRDI 命令に続く CS の立ち上がりエッジでクリアされます。

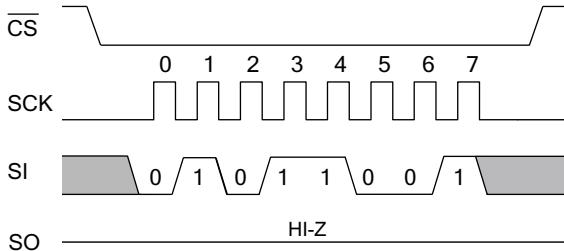

**図 10. WRDI 命令**

### プロック保護

プロック保護は状態レジスタの BP0 および BP1 ピンを使用して提供されます。これらのビットは WRSR 命令を使用して設定でき、RDSR 命令を使用してプローブすることができます。nvSRAM は 4 つのアレイセグメントに分割されます。1/4、1/2、またはすべてのメモリセグメントを保護することができます。保護されたセグメント内のすべてのデータは読み取り専用となります。**表 4** にプロック保護ビットの機能が示されています。

**表 4. プロック書き込み保護ビット**

| Level<br>(レベル) | ステータス レジスタ<br>ビット |     | 保護されたアレイ<br>アドレス |

|----------------|-------------------|-----|------------------|

|                | BP1               | BP0 |                  |

| 0              | 0                 | 0   | なし               |

| 1 (1/4)        | 0                 | 1   | 0x18000–0x1FFFF  |

| 2 (1/2)        | 1                 | 0   | 0x10000–0x1FFFF  |

| 3 (すべて)        | 1                 | 1   | 0x00000–0x1FFFF  |

### ハードウェア書き込み保護 (WP ピン)

書き込み保護ピン (WP) は、ハードウェア書き込み保護を提供するために使用されます。WP ピンが HIGH に維持された時、すべて通常の読み取りと書き込みオペレーションが可能となります。WP ピンが LOW に下げられ、WPEN ビットが「1」になった時、状態レジスタへのすべての書き込み動作が禁止されます。WPEN ビットが「0」の時、ハードウェア書き込み保護

機能がブロックされます。これにより、WP ピンがグランドに接続している状態でシステムにデバイスをインストールすることができ、状態レジスタに書き込むこともできます。

メモリへの書き込みを禁止するために、WP ピンを状態レジスタの WPEN およびブロック保護ビット (BP1 と BP0) と一緒に使用することができます。WP ピンが LOW で WPEN が「1」に設定されていると、状態レジスタへの変更はディスエーブルになります。したがって、BP0 および BP1 ビットに設定することによってメモリが保護され、WP ピンがハードウェア書き込み保護を提供して、状態レジスタビットの変更が禁止されます。

**注** CS がまだ LOW の状態で WP が LOW になっても、状態レジスタへの進行中の書き込みオペレーションへの影響は何もありません。

**表 5** すべての保護機能は、CY14X101PA に一覧されています。

**表 5. 書き込み保護動作**

| WPEN | WP   | WEN | 保護されて<br>いる<br>ブロック | 保護されてい<br>ないブロック | 状態レジスタ |

|------|------|-----|---------------------|------------------|--------|

| X    | X    | 0   | 保護                  | 保護               | 保護     |

| 0    | X    | 1   | 保護                  | 書き込み可能           | 書き込み可能 |

| 1    | LOW  | 1   | 保護                  | 書き込み可能           | 保護     |

| 1    | HIGH | 1   | 保護                  | 書き込み可能           | 書き込み可能 |

### メモリアクセス

すべてのメモリアクセスは、READ および WRITE 命令を使用して行われます。STORE または RECALL サイクルが進行中は、これらの命令を使用することはできません。進行中の STORE サイクルは、状態レジスタの RDY および HSB ピンのビットによって示されます。

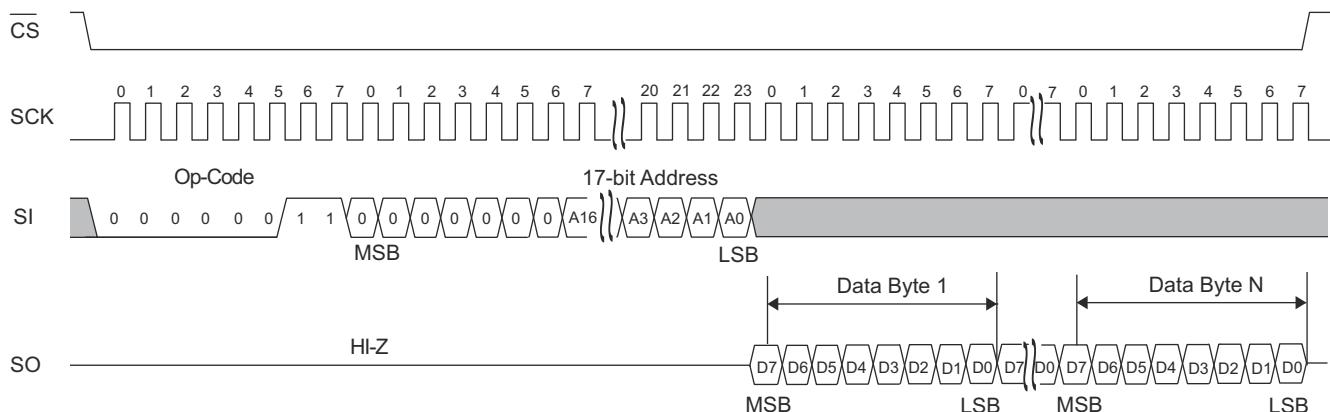

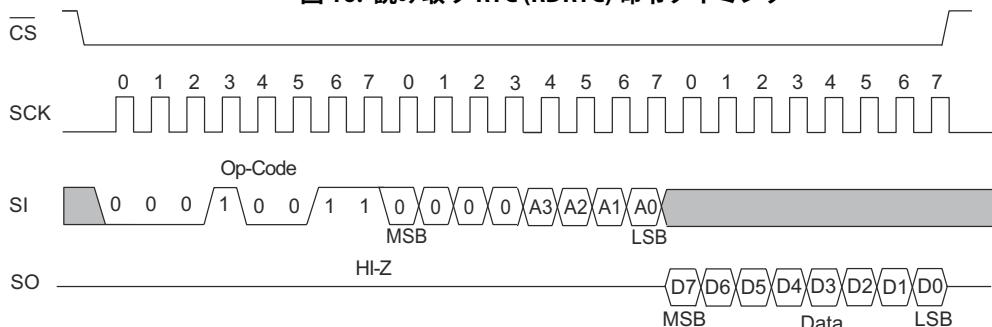

### 読み取りシーケンス (READ) 命令

CY14X101PA の読み取りオペレーションは、SI ピンに命令を与え、SO ピンの出力を読み取ることによって実行されます。次のシーケンスの後には読み取りオペレーションが続く必要があります。デバイスを選択するために CS ラインが LOW にプルダウンされると、読み取りオペコードが SI ラインを介して送信され、その後にアドレスの 3 バイト (A12-A0) が続きます。最上位アドレスバイトにはビット 0 に A16 が含まれていて、他のビットは「ドント・ケア」です。アドレスビット A15 ~ A0 が次の 2 つのアドレスバイトで送信されます。最後のアドレスビットが SI ピンに送信された後、特定のアドレス位置のデータ (D7-D0) が D7 で始まる SCK の立ち下がりエッジで SO ピンにシフトアウトされます。最後のアドレスビットの後の SI ライン上の他のデータは無視されます。

CY14X101PA では、SPI を介してバーストで読み取りを実行することができる所以、これにより新しい READ 命令を発行せずに、連続したアドレス上で読み取り処理を実行できます。1 バイトだけが読み取られる場合、1 バイトのデータが出てきた後、CS ラインは HIGH に駆動される必要があります。しかし、読み取りシーケンスは CS ラインを LOW に保持することによって継続することができ、アドレスは自動的にインクリメントされ、データの SO ピンへのシフトアウトも継続されます。最後のデータメモアドレ (0x1FFF) に到達すると、アドレスは 0x00000 にロールオーバーし、デバイスは読み取りを継続します。

**注** READ 命令は最大の 40MHz SPI 周波数まで動作します。

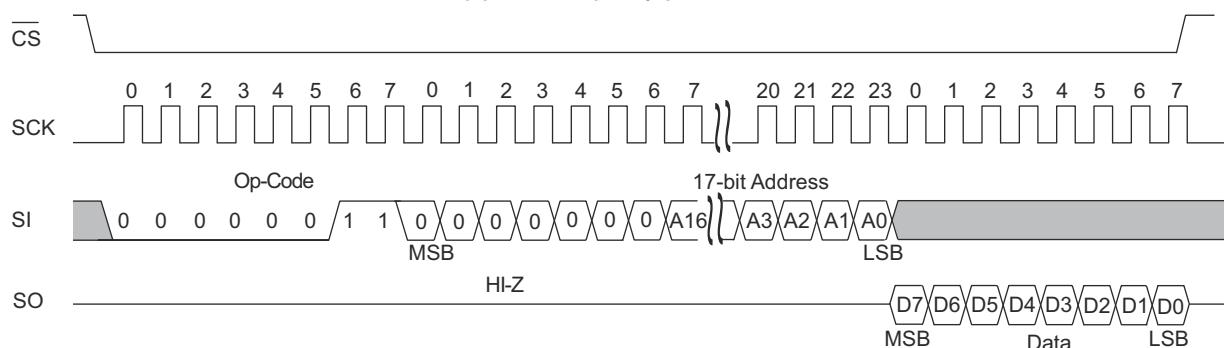

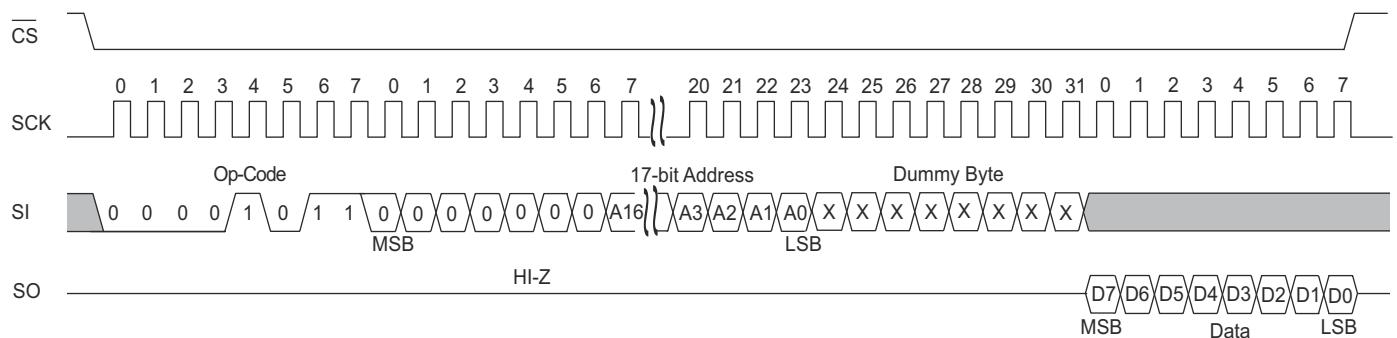

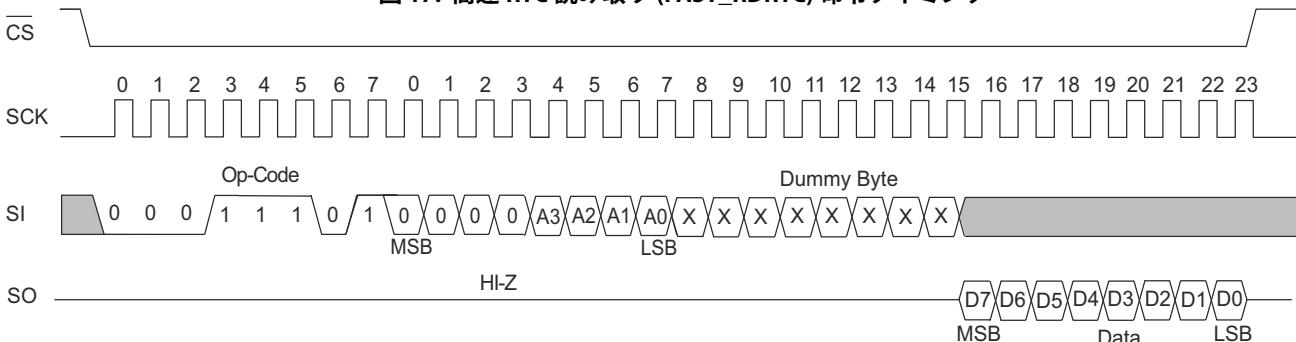

### 高速読み取りシーケンス (FAST\_READ) 命令

FAST\_READ 命令により、SPI 周波数 40MHz 以上および最大 104MHz (最大)まで、メモリを読み取ることができます。ホストシステムは、最初に CS を LOW に駆動することでデバイスを選択する必要があります、そして FAST\_READ 命令が SI に書き込まれ、17 ビットアドレス (A16 ~ A0) およびその後に続くダミーバイトを含む 3 つのアドレスバイトが続きます。

次の SCK 立ち下がりエッジから、MSB から始まる SO ラインで特定アドレスのデータがシリアルでシフトアウトされます。指定される最初のバイトは、どの位置でもかまいません。データの各バイトが出力された後、デバイスが次の上位アドレスに自動的にインクリメントします。したがって、メモリアレイ全体を単一の FAST\_READ 命令で読み取ることができます。メモリアレイの最上位アドレスに到達すると、アドレスカウンタはアドレス 0x00000 を開始するようにロールオーバーされるため、読み取りシーケンスが永久に続行されます。FAST\_READ 命令は、データ出力中の任意の時点で CS が HIGH に駆動されることで終了されます。

注 FAST\_READ 命令は最大の 104MHz SPI 周波数まで動作します。

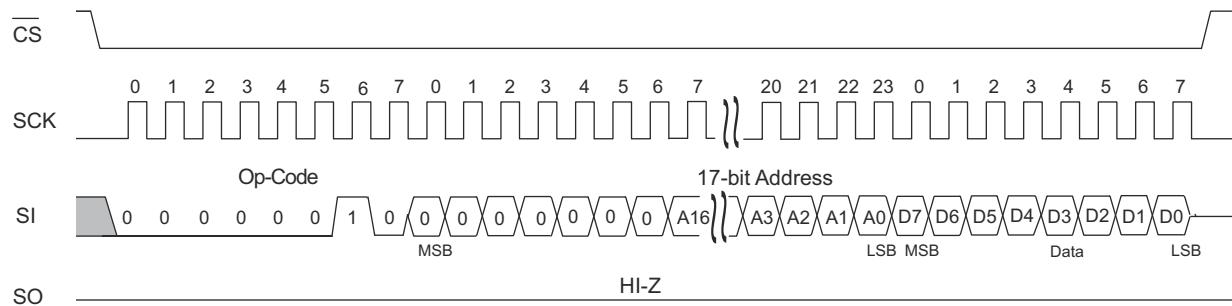

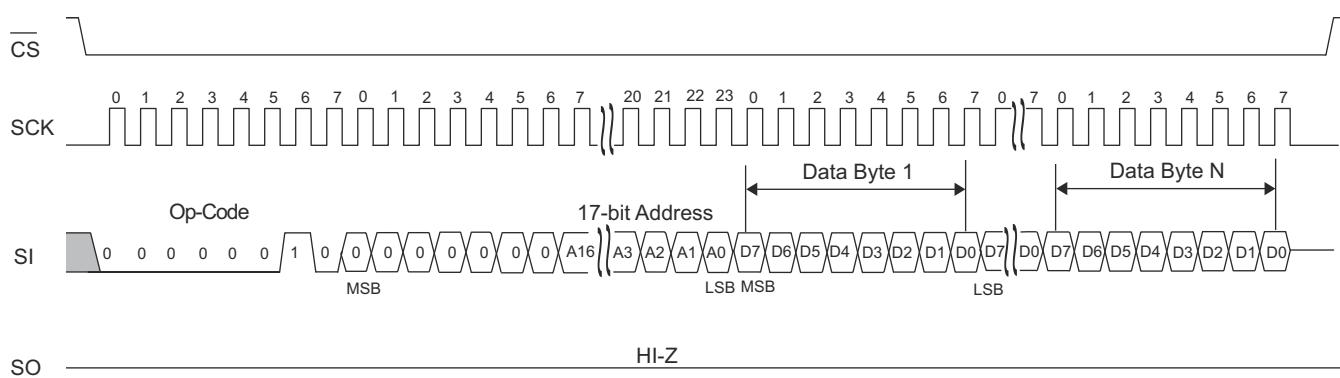

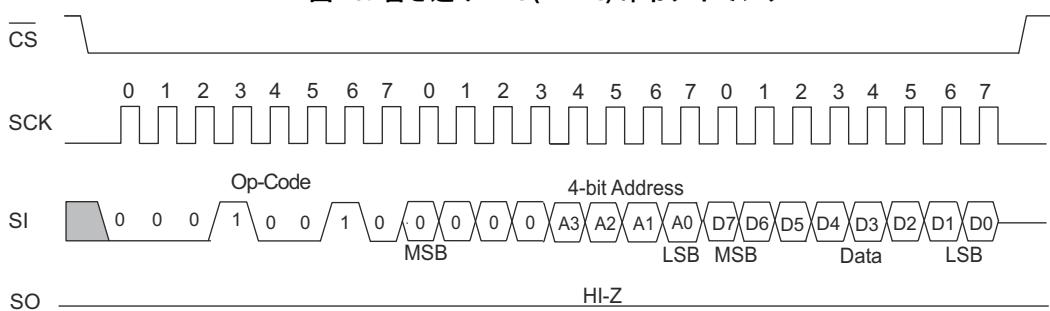

### 書き込みシーケンス (WRITE) 命令

CY14X101PA の書き込みオペレーションは、SI ピンを介して実行されます。デバイスが書き込みディスエーブルである場合に書き込みオペレーションを実行するには、まずデバイスを書き込み WREN 命令を使用してイネーブルにする必要があります。書き込みがイネーブル (WEN=「1」) にされると、CS の立

ち下がりエッジ後に WRITE 命令が発行されます。WRITE 命令は SI ライン上の WRITE オペコードの送信を構成し、その後アドレスの 3 つのバイトおよび書き込まれるデータ (D7-D0) が続きます。最上位アドレスバイトにはビット 0 に A16 が含まれていて、他のビットは「ドント・ケア」です。アドレスビット A15 ~ A0 が次の 2 つのアドレスバイトで送信されます。

CY14X101PA では、SPI を介してバーストで書き込みを実行することができるでの、これにより新しい WRITE 命令を発行せずに、連続したアドレス上で書き込み処理を実行できます。1 バイトだけが書き込まれる場合、D0 (データの LSB) が送信された後、CS ラインは HIGH に駆動される必要があります。より多くのバイトが書き込まれる場合は、CS ラインを LOW に保持しなければならず、アドレスは自動的にインクリメントされます。SI ラインの次のバイトはデータバイトとして扱われ、連続したアドレスに書き込まれます。最後のデータメモリアドレス (0xFFFF) に到達すると、アドレスは 0x00000 にロールオーバーし、デバイスは書き込みを継続します。

書き込みシーケンスの完了時に WEN ビットは「0」にリセットされます。

注 バースト書き込みが保護されたブロックアドレスに到達すると、それは保護された空間にアドレスのインクリメントを継続しますが、保護されたメモリにデータが書き込まれることはありません。アドレスのロールオーバーにより保護されていない空間にバースト書き込みがなされる場合、書き込みが再開されます。バースト書き込みが書き込み保護されたブロック内で開始された場合は、同じオペレーションは true となります。

図 11. 読み取り命令タイミング

図 12. バーストモード読み取り命令タイミング

**図 13. 高速読み取り命令タイミング**

**図 14. 書き込み命令タイミング**

**図 15. バーストモード書き込み命令タイミング**

## RTC アクセス

CY14X101PA は、RTC に 16 レジスタを使用します。バーストモードで 16 すべてのレジスタにアクセスする、または各レジスタに 1 つずつアクセスすることで、これらのレジスタへの読み書きを行うことができます。RDRTC、FAST\_RDRTC、およびWRTC 命令は、RTC にアクセスするために使用されます。

RDRTC および FAST\_RDRTC 命令を発行して、CS ピンを HIGH に駆動することなく 16 バイトすべてを読み取ることで、すべての RTC レジスタをバーストモードで読み取ることができます。時間の過渡的な値が読み込まれないようにするために、RTC 時間保持レジスタの読み取り中は「R」ビットが設定されている必要があります。

RTC レジスタへの書き込みは、WRTC 命令を使用して実行されます。フラグを除き、RTC 時間保持レジスタと制御レジスタへの書き込みの際に、フラグレジスタの「W」ビットが「1」に設定されている必要があります。「W」ビットが「0」にクリアされた時に、内部カウンタが新しい日付と時間設定で更新されます。WRTC 命令を使用して、バーストモードですべての RTC レジスタに書き込むこともできます。

### 読み取り RTC (RDRTC) 命令

読み取り RTC (RDRTC) 命令により、SPI 周波数最大 25MHz まで、RTC レジスタのコンテンツを読み取ることができます。SO ピンを通して RTC レジスタを読み取るには、次のシーケンスが必要です。デバイスを選択するために CS ラインが LOW にプルダウンされると、RDRTC オペコードが SI ラインを介して送信され、レジスタ選択のためにその後にアドレスの 8 バイトが続きます。アドレスビットの後の SI ラインのデータはすべて無視されます。そして、指定されたアドレスのデータ (D7-D0) は、SO ラインにシフトアウトされます。RDRTC では、バーストモードでの読み取りオペレーションも可能です。RTC レジスタから複数バイトを読み取る際、最後の RTC レジスタアドレス (0x0F) に達すると、アドレスは 0x00 にロールオーバーします。

図 16. 読み取り RTC (RDRTC) 命令タイミング

図 17. 高速 RTC 読み取り (FAST\_RDRTC) 命令タイミング

### 書き込み RTC (WRTC) 命令

書き込み RTC (WRTC) 命令により、RTC レジスタのコンテンツを変更することができます。WRTC 命令が発行される前に、WEN ビットが「1」に設定されている必要があります。WEN ビットが「0」になっている場合は、WRTC を使用する前に、WREN 命令が発行される必要があります。RTC レジスタへの書き込みには、次のシーケンスが必要です。デバイスを選択するために CS ラインが LOW にプルダウンされた後、WRTC オペコードが SI ラインを介して送信され、その後書き込まれるレジスタを識別する 8 つのアドレスビットおよびデータの 1 つま

たは複数のバイトが続きます。WRTC ではバーストモードでの書き込みオペレーションが可能です。バーストモードで複数のレジスタを書き込む際には、最後の RTC アドレス (0x0F) に達した後、アドレスは 0x00 にロールオーバーされます。

RTC 時間保持および制御レジスタへの書き込みでは、W ビットが「1」に設定されている必要があることに注意してください。これらの RTC レジスタの値は、「W」ビットが「0」にクリアされた後にのみ効力を発します。書き込みイネーブルビット (WEN) は、WRTC 命令が完了した後、自動的に「0」にクリアされます。

図 18. 書き込み RTC (WRTC) 命令タイミング

### nvSRAM 特別命令

CY14X101PA は、nvSRAM の特定機能へのアクセスを可能にする次の 4 つの特別命令を提供します。STORE、RECALL、ASDISB、および ASENB です。これらの命令は表 6 に一覧されています。

表 6. nvSRAM 特別命令

| 関数名    | オペレーションコード | 動作                |

|--------|------------|-------------------|

| STORE  | 0011 1100  | ソフトウェア STORE      |

| RECALL | 0110 0000  | ソフトウェア RECALL     |

| ASENB  | 0101 1001  | AutoStore イネーブル   |

| ASDISB | 0001 1001  | AutoStore ディスエーブル |

### ソフトウェア STORE (STORE) 命令

STORE 命令が実行されると、CY14X101PA はソフトウェア STORE オペレーションを実行します。STORE オペレーションは、最後の STORE または RECALL オペレーション以降に書き込みが行われたかどうかに関係なく実行されます。

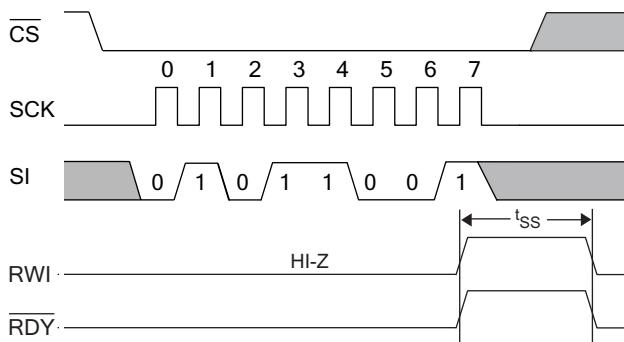

図 19. ソフトウェア STORE 動作

この命令を発行するには、デバイスは書き込みイネーブル (WEN ビット = 「1」) になっている必要があります。命令は CS の立ち下がりエッジの後に SI ピンの STORE オペコードが送信されることで実行されます。STORE 命令後の CS ポジティブエッジで WEN ビットがクリアされます。

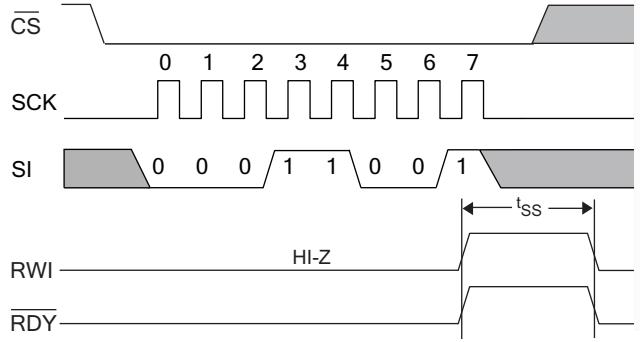

### ソフトウェア RECALL (RECALL) 命令

RECALL 命令が実行されると、CY14X101PA がソフトウェア RECALL オペレーションを実行します。この命令を発行するには、デバイスは書き込みイネーブル (WEN=「1」) になっている必要があります。

命令は CS の立ち下がりエッジの後に SI ピンの RECALL オペコードが送信されることで実行されます。RECALL 命令後の CS ポジティブエッジで WEN ビットがクリアされます。

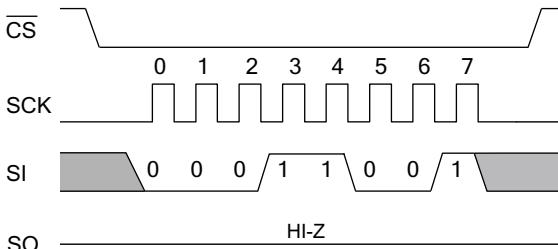

図 20. ソフトウェア RECALL 動作

### AutoStore イネーブル (ASENB) 命令

AutoStore イネーブル命令により、CY14X101PA の AutoStore がイネーブルとなります。この設定は不揮発性ではなく、これがパワーサイクルで耐えられるようにするには、その後に STORE シーケンスを行う必要があります。

この命令を発行するには、デバイスは書き込みイネーブル (WEN = 「1」) になっている必要があります。命令は CS の立ち下がりエッジの後に SI ピンの ASENB オペコードが送信される

ことで実行されます。ASENB 命令後の  $\overline{CS}$  ポジティブエッジで WEN ビットがクリアされます。

図 21. AutoStore イネーブル動作

### AutoStore ディスエーブル (ASDISB) 命令

AutoStore は CY14X101PA のデフォルトでイネーブルになります。AutoStore ディスエーブル命令は CY14X101PA の AutoStore をディスエーブルにします。この設定は不揮発性ではなく、これがパワーサイクルで耐えられるようにするには、その後に STORE シーケンスを行う必要があります。

この命令を発行するには、デバイスは書き込みイネーブル (WEN=「1」) になっている必要があります。命令は  $\overline{CS}$  の立ち下がりエッジの後に SI ピンの ASDISB オペコードが送信されることで実行されます。ASDISB 命令後の  $\overline{CS}$  のポジティブエッジで WEN ビットがクリアされます。

図 22. AutoStore ディスエーブル動作

## 特別命令

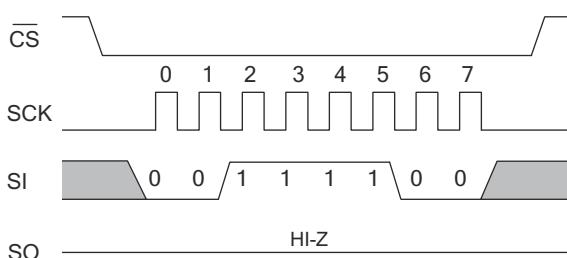

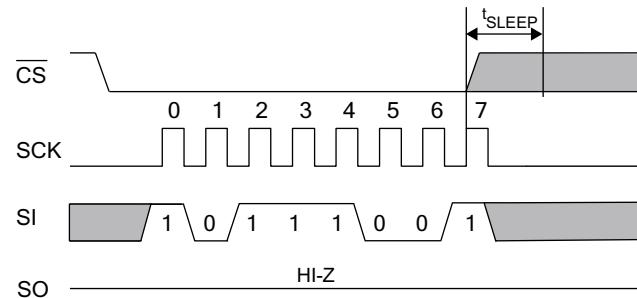

### SLEEP 命令

SLEEP 命令により、nvSRAM はスリープモードとなります。SLEEP 命令が発行されると、nvSRAM は  $t_{SS}$  時間を取り SLEEP 要求を処理します。一旦 SLEEP コマンドが正常に取り込まれて処理されると、nvSRAM は HSB を LOW にトグルし、不揮発性メモリにデータを確実に保全するために STORE オペレーションを実行してから、スリープモードに入ります。デバイスは SLEEP 命令が取り込まれると、インスタンスからの  $t_{SLEEP}$  時間後に  $I_{ZS}$  電流を消費し始めます。SLEEP 命令が出された後は、通常のオペレーションではデバイスにアクセスすることができなくなります。一旦スリープモードになると、SCK および SI ピンは無視され、SO は Hi-Z になりますが、デバイスは CS ピンの監視を継続します。

スリープモードから nvSRAM をウェイクさせるには、 $\overline{CS}$  ピンを HIGH から LOW にトグルしてデバイスが選択される必要があります。 $\overline{CS}$  ピンの立ち下がりエッジが検出された後、 $t_{WAKE}$  期間が経過すると、デバイスはウェイクアップし、通常のオペレーションでアクセス可能となります。

**注** nvSRAM がスリープモードに入る際は常に不揮発性 STORE サイクルを開始し、その結果として SLEEP コマンド実行のたびに耐久サイクルをもたらします。STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始されます。

図 23. スリープモードへの移行

## シリアル番号

シリアル番号はこのデバイスを一意に識別するためにユーザーに提供される 8 バイトのプログラマブルメモリ空間です。それは典型的に 2 バイトのカスタマ ID、その後に続く固有の 5 バイトのシリアル番号と CRC チェックの 1 バイトで構成されています。しかし、nvSRAM は CRC を計算しないため、所望の形式で 8 バイトのメモリ空間を利用するかどうかはシステム設計者次第となります。8 バイトの位置のデフォルト値は「0x00」に設定されています。

### WRSN (シリアル番号書き込み) 命令

シリアル番号は WRSN 命令を使用して書き込むことができます。シリアル番号を書き込むには、WREN 命令を使用して書き込みがイネーブルになっている必要があります。WRSN 命令は、シリアル番号の 8 バイトすべてを書き込むためにバーストモードで使用することができます。

シリアル番号は、状態レジスタの SNL ビットを使用してロックされます。一旦このビットが「1」に設定されると、シリアル番号に変更を加えることはできなくなります。SNL ビットが「1」に設定された後は、WRSN 命令の使用はシリアル番号に影響を与えません。

シリアル番号を不揮発性メモリに格納するには、STORE オペレーション (AutoStore またはソフトウェア STORE) が必要です。AutoStore がディスエーブルになっている場合は、ソフトウェア STORE オペレーションを実行して、シリアル番号を確保しロックする必要があります。SNL ビットが「1」に設定されていて格納(AutoStore ディスエーブル)されていない場合は、次のパワーサイクル時に SNL ビットとシリアル番号はデフォルトで「0」となります。SNL ビットが「1」に設定されていて格納されている場合は、SNL ビットを「0」にクリアすることはできません。この命令では、それが実行される前に WEN ビットが設定されている必要があります。この命令の完了後、WEN ビットは「0」にリセットされます。

**図 24. WRSN 命令**

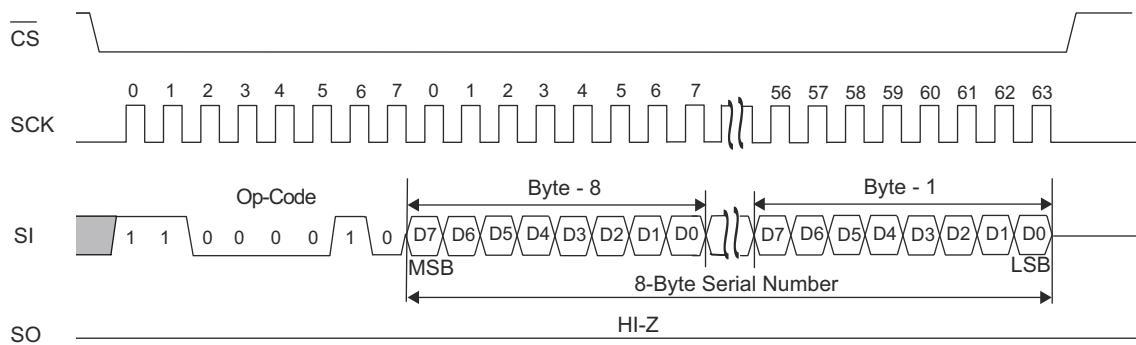

### RDSN (シリアル番号読み取り) 命令

シリアル番号は最大 40MHz の SPI 周波数で RDSN 命令を使用して読み取られます。シリアル番号読み取りは、バーストモードで実行して一度にすべての 8 バイトを読み取ることができます。シリアル番号の最後のバイトが読み取られた後は、デバイスはループバックしません。CS が LOW になった後、nvSRAM の SI ピン経由で RDSN のオペレーションコードをシフトすることによって、RDSN 命令を発行することができます。この後、nvSRAM が SO ピンを介してシリアル番号の 8 バイトをシフトアウトします。

**図 25. RDSN 命令**

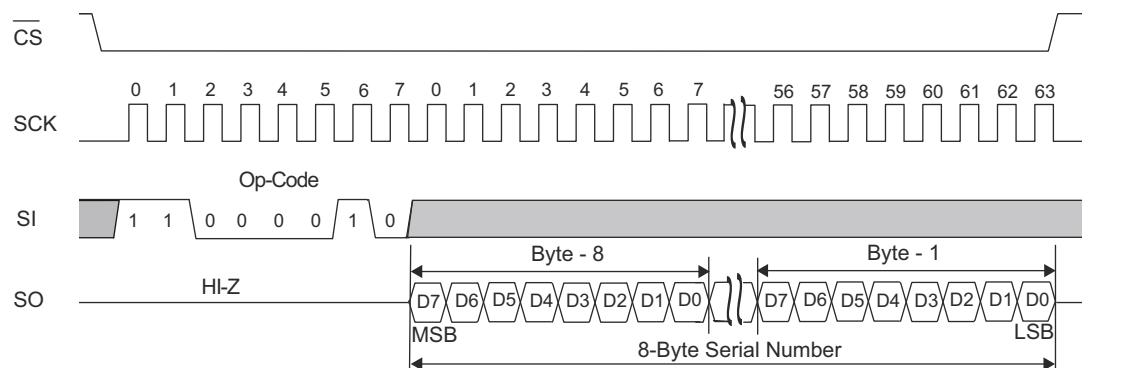

### FAST\_RDSN (高速シリアル番号読み取り) 命令

FAST\_RDSN 命令は、SPI 周波数 40MHz 以上、最大 104MHz(最大)でシリアル番号を読み取るために使用されます。シリアル番号読み取りは、バーストモードで実行して一度にすべての 8 バイトを読み取ることができます。シリアル番号の最後のバイトが読み取られた後は、デバイスはループバックしません。CS が LOW になった後、nvSRAM の SI ピン経由で FAST\_RDSN のオペレーションコードをシフトし、その後にダミーバイトが続くことで FAST\_RDSN 命令を発行することができます。その後、nvSRAM が SO ピンを介してシリアル番号の 8 バイトをシフトアウトします。

**図 26. FAST\_RDSN 命令**

## デバイス ID

デバイス ID は一意に製品の種類を識別するための 4 バイトの読み取り専用コードです。これには、製品の製品ファミリコード、構成、および容量が含まれています。

表7. デバイス ID

| デバイス       | デバイス ID<br>(4 バイト) | デバイス ID の説明       |                  |                |                |

|------------|--------------------|-------------------|------------------|----------------|----------------|

|            |                    | 31-21<br>(11 ビット) | 20-7<br>(14 ビット) | 6-3<br>(4 ビット) | 2-0<br>(3 ビット) |

|            |                    | メーカー ID           | 製品 ID            | 容量 ID          | ダイ改訂           |

| CY14C101PA | 0x0681C0A0         | 00000110100       | 00001110000001   | 0100           | 000            |

| CY14B101PA | 0x0681C8A0         | 00000110100       | 00001110010001   | 0100           | 000            |

| CY14E101PA | 0x0681D0A0         | 00000110100       | 00001110100001   | 0100           | 000            |

表7 に示されているように、デバイス ID は 4 つの部分に分かれています。

### 1. メーカー ID (11 ビット)

これはサイプレス用に JEDEC が割り当てたメーカーの ID です。JEDEC は異なるバンクでメーカー ID を割り当てます。メーカー ID の最初の 3 ビットは、ID が割り当てられているバンクを表しています。次の 8 ビットはメーカー ID を表しています。サイプレスのメーカー ID はバンク 0 の 0x34 です。したがって、すべてのサイプレスの nvSRAM 製品のメーカー ID は以下のようになっています。

サイプレス ID - 000\_0011\_0100

### 2. 製品 ID (14 ビット)

デバイスの製品 ID は表7 に示されています。

### 3. 容量 ID (4 ビット)

表7 に示されているように、4 ビットの容量 ID は製品の 1Mb 容量を示しています。

### 4. ダイ改訂 (3 ビット)

これは製品の設計への大幅な変更を表すために使用されます。初期設定は常に 0x0 です。

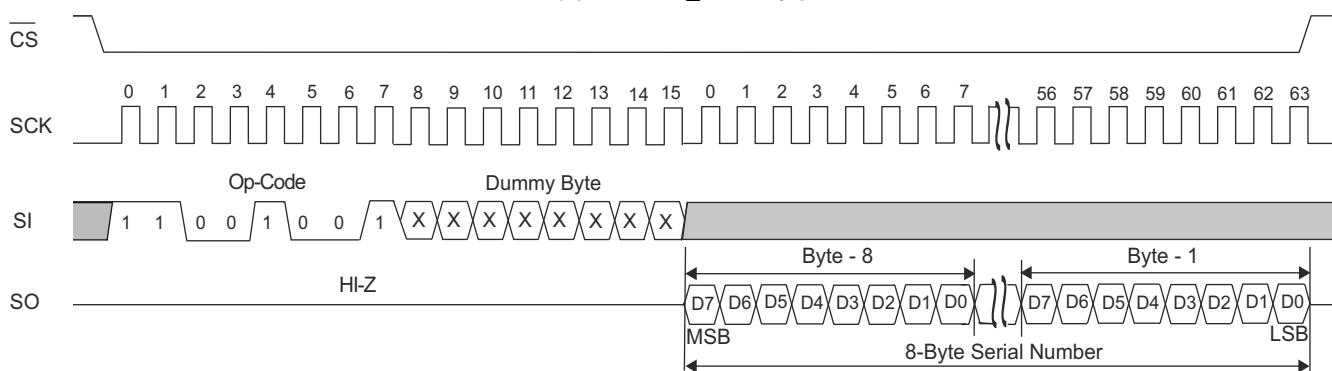

## RDID (デバイス ID 読み取り) 命令

この命令は、JEDEC 割り当てのメーカー ID とデバイスの製品 ID を SPI 周波数最大 40MHz で読み取るために使用されます。この命令は、バス上のデバイスを識別するためにも使用することができます。CS が LOW になった後、nvSRAM の SI ピン経由で RDID のオペレーションコードをシフトすることによって、RDID 命令を発行することができます。この後、nvSRAM が SO ピンを介してデバイス ID の 4 バイトをシフトアウトします。

図 27. RDID 命令

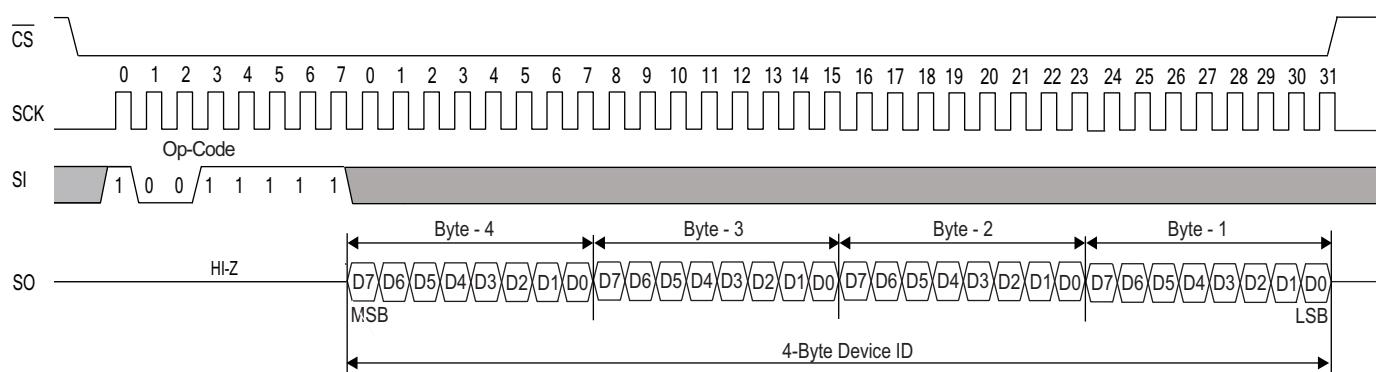

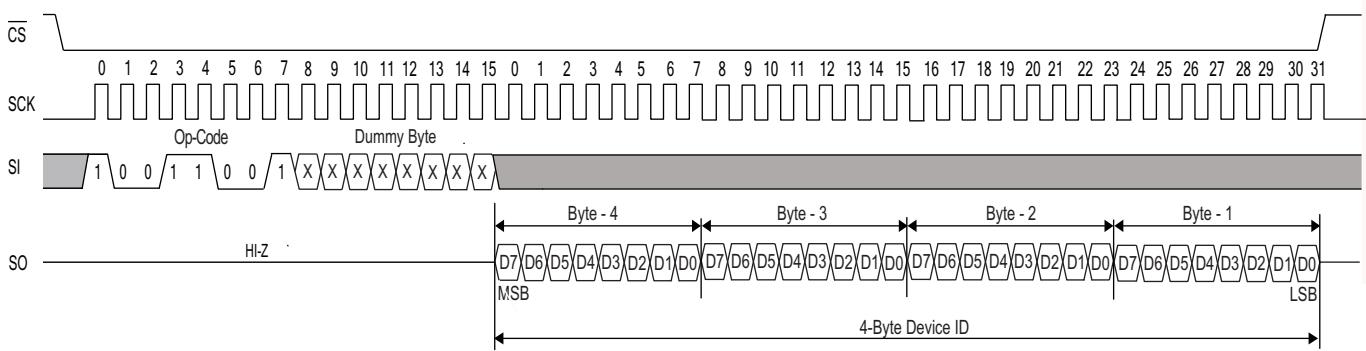

### FAST\_RID (高速デバイス ID 読み取り) 命令

FAST\_READ 命令により、SPI 周波数 40MHz 以上および最大 104MHz (最大)まで、JEDEC 割り当てのメーカー ID と製品 ID を読み取ることができます。CS が LOW になった後、nvSRAM の SI ピン経由で FAST\_RID のオペレーションコードをシフトし、その後にダミーバイトが続くことで FAST\_RID 命令を発行することができます。この後、nvSRAM が SO ピンを介してデバイス ID の 4 バイトをシフトアウトします。

図 28. FAST\_RID 命令

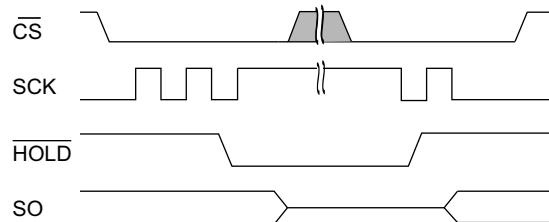

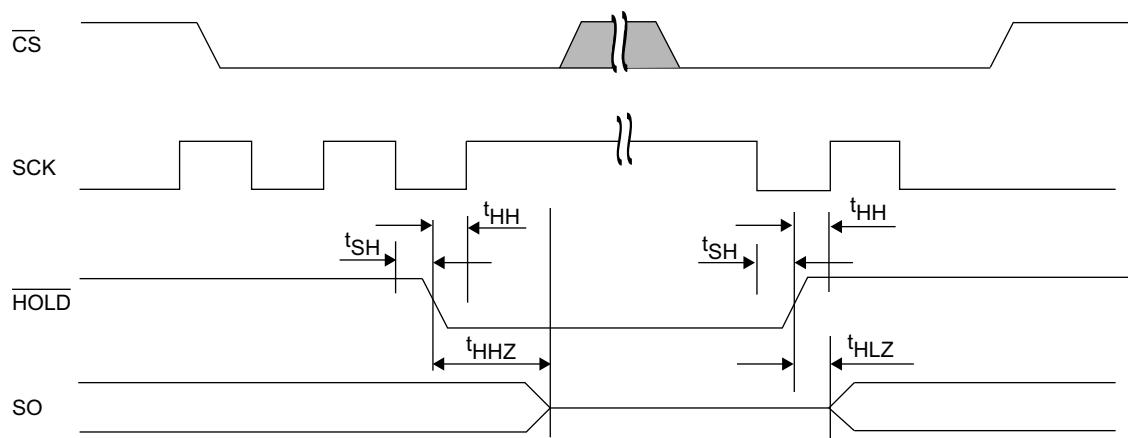

### HOLD ピン動作

HOLD ピンはシリアル通信を一時停止するために使用されます。デバイスが選択されていて、シリアルシーケンスが進行中の場合、HOLD は現在進行中のシリアルシーケンスをリセットすることなく、マスタデバイスでシリアル通信を一時停止するために使用されます。一時停止するには、SCK ピンが LOW の時に HOLD ピンが LOW に下げる必要があります。シリアル通信を再開するには、SCK ピンが LOW の時に HOLD ピンを HIGH にする必要があります (SCK は HOLD 中トグルする場合があります)。デバイスのシリアル通信が一時停止している間、SI ピンへの入力は無視され、SO ピンはハイインピーダンス状態となります。

このピンは、シリアル通信をリセットすることなく、HOLD ピンを LOW にすることによってシリアル通信を一時停止するため、および SPI スレーブを選択解除することによって他のスレーブデバイスとの通信を確立するために、CS ピンとともにマスターによって使用されます。デバイスが選択され、HOLD ピンが HIGH に設定された時点で、通信を再開することができます。

図 29. HOLD 動作

## リアルタイム クロック

### nvTIME の動作

CY14X101PA には、クロック、アラーム、ウォッチドッグ、割り込み、および制御機能を含む内部レジスタがあります。RTC レジスタは nvSRAM からの独立したアドレス空間を占有し、レジスタアドレス 0x00～0x0F の読み取り RTC レジスタおよび書き込み RTC レジスタのシーケンスを介してアクセスできます。時間保持レジスタの内部ダブルバッファは、読み取りまたは書き込みオペレーション中の過渡的な内部クロックデータへのアクセスを防ぎます。またダブルバッファリングは、外部からクロック データにアクセスする際、通常のタイミング カウントの中止させず、クロック精度の劣化を回避します。クロックおよびアラーム レジスタは BCD 形式でデータをストアします。

### クロックの動作

クロックレジスタは、1 秒単位で 9,999 年までの時間を維持します。時刻は任意のカレンダー時間に設定することができ、クロックは曜日と月の日、うるう年、世紀の遷移を自動的に刻みます。クロック機能には 8 つの専用レジスタがあります。これは書き込みサイクルで時間を設定し、読み取りサイクルで時間を読み取ります。これらのレジスタには BCD 形式で時間が含まれます。「0」として定義されたビットは、現在使用されておらず、将来使用するために予約されています。

### クロックの読み込み

ダブルバッファ RTC レジスタの構造は、クロックから不正なデータを読み取る可能性を減らします。遷移におけるデータの読み取りを防止するために、CY14X101PA 時間保持レジスタの内部更新は、読み取りクロックデータの前に、読み取りビット「R」(フラグレジスター - 0x00) が「1」に設定されると停止されます。レジスタの更新停止は、クロックの精度に影響を与えません。

RTC デバイスの読み取りシーケンスが開始されると、ユーザーの時間保持レジスタの更新が停止され、「0」が読み取りビット「R」(フラグレジスターの 0x00) に書き込まれるまで再開されません。読み取りシーケンスの終了後、すべての RTC レジスタが、20ms 以内に同時に更新されます。

### クロックの時刻設定

書き込みビット「W」(フラグレジスター 0x00) が「1」に設定されると、RTC デバイスへの書き込みアクセスが時間保持レジスタの更新を停止し、時間の設定を可能にします。次に、正しい曜日、日付、および時間がレジスタに書き込まれます。正しい形式は、24 時間 BCD 形式です。書き込まれた時間は、「基準時刻」と呼ばれます。この値は、不揮発性レジスタに格納され、現在の時刻の計算に使用されます。「0」が書き込まれて書き込みビット「W」がクリアされると、クロックが通常のオペレーションを再開した後、時間保持レジスタの値は実際のクロックカウンタに転送されます。

時間保持レジスタに書き込まれた時間が正しい BCD 形式でない場合は、RTC レジスタの各無効ニブルは、RTC が通常のオペレーションを再開した後で、0x0 にロールオーバーする前に、0xF までカウントを継続します。

注 「W」ビットが「0」に設定された後、時間保持、アラーム、校正、および割り込みレジスタに書き込まれる値は、 $t_{RTCP}$  時間で RTC 時間保持カウンタに転送されます。これらのカウンタの値は、ソフトウェア/ハードウェア STORE または AutoStore オペレーションを開始することにより、不揮発性メモリに保存する必要があります。AutoStore をディスエーブルにしたモードでは、変更が正しく記録されるよう、RTC レジスタへの書き

込みを行なながら、 $t_{RTCP}$  時間の後に STORE オペレーションを実行してください。

### バックアップ電源

CY14X101PA の RTC は、永続的電源供給オペレーション用に設計されています。用途に応じバックアップ電源にコンデンサかバッテリを選択します。これにより  $V_{RTCcap}$  または  $V_{RTChat}$  ピンを使用します。主電源が供給されている時、 $V_{CC}$  が異常になり、 $V_{SWITCH}$  を下回ると、デバイスは電源をバックアップ電源に切り替えます。

クロック発振器の消費電流は非常に小さいため、バックアップ電源によるバックアップ時間が長くなります。主電源を喪失した状態のクロックオペレーションにかかわらず、nvSRAM に格納されたデータは電源が失われたときに不揮発性素子に格納されるため、データが失われることはできません。

バックアップオペレーション中に、CY14X101PA は室温で 0.45  $\mu$ A (代表値) を消費します。ユーザは、用途に応じてコンデンサやバッテリの値を選択する必要があります。

最大電流仕様に基づくバックアップ時間の値が、以下の表 8 に示されています。公称バックアップ時間は約 2 倍長くなります。

表 8. RTC のバックアップ時間

| コンデンサの値 | バックアップ時間<br>(CY14B101PA) |

|---------|--------------------------|

| 0.1F    | 60 時間                    |

| 0.47F   | 12 日                     |

| 1.0F    | 25 日                     |

コンデンサを使用すると、システムの電源が投入されるたびにバックアップ電源が充電されるという明白な利点があります。バッテリを使用する場合は、3V リチウムバッテリをお勧めします。CY14X101PA は、主電源が取り去られた場合に、バッテリからの電流を受けます。ただし、バッテリは、CY14X101PA によって常に充電されるわけではありません。バッテリ容量は、システムのライフサイクルを通して、必要なダウンタイムの合計予想時間を考慮して選択する必要があります。

### 発振器の起動と停止

0x08 制御にある校正レジスタの OSCEN ビットが、発振器のイネーブルまたはディスエーブルを制御します。このビットは不揮発性であり、「イネーブル状態」(「0」に設定されている) でお客様に出荷されます。システムが保存状態にある場合にバッテリを保たせるには、OSCEN を「1」に設定する必要があります。これにより発振回路が停止し、バッテリ寿命が延長されます。OSCEN ビットがディスエーブルからイネーブルになる場合は、発振器が開始されるのに約 1 秒 (最大 2 秒) かかります。システムの電源がオフである時にバックアップ電源の電圧 ( $V_{RTCcap}$  または  $V_{RTChat}$ ) がそれぞれの最小レベルを下回ると、発振器が動作しなくなることがあります。CY14X101PA には、システム電源が回復された時に、発振器の異常を検出する能力があります。これは、アドレス 0x00 にあるフラグレジスタの発振器異常フラグ (OSCF) に記録されます。デバイスに電流が供給されている ( $V_{CC}$  が  $V_{SWITCH}$  を上回る) 場合、OSCEN ビットがチェックされ、「イネーブル」状態であることが確認されます。OSCEN ビットがイネーブルになつていて、発振器が最初の 5ms 以内に起動しない場合は、OSCF ビットが「1」に設定されます。システムはこの条件を点検し、フラグをクリアするために「0」を書き込む必要があります。

OSCF フラグビットを設定することに加え、時間レジスタが「基準時刻」にリセットされることに注意してください。この時間は、時間保持レジスタに書き込まれる最後の値です。制御ま

たは校正レジスタと OSCEN ビットは、「発振器異常」コンディションによる影響は受けません。

OSCF の値は、時間レジスタが最初に書き込まれた際に、「0」にリセットする必要があります。これは、システムが最初に電源を投入された時に設定されている可能性があり、このビットの状態を初期化します。

OSCF をリセットするには、書き込みビット「W」( フラグレジスタ – 0x00) を「1」に設定し、フラグレジスタへの書き込みをイネーブルにします。書き込みをディスエーブルにするには、OSCF に「0」を書き込み、書き込みビットを「0」にリセットします。

## クロックの校正

RTC は 32.768kHz の公称周波数を持つクオーツ水晶によって駆動されます。クロックの精度は、水晶と校正の品質に依存します。市場で入手可能な水晶は、通常、 $\pm 20 \text{ ppm} \sim \pm 35 \text{ ppm}$  の誤差を持ちます。ただし、CY14X101PA は 25°C で +1/-2ppm まで精度を向上させる校正回路を採用しています。これは、月当たり +2.5 ~ -5 秒の誤差を意味します。

校正回路は、この精度を達成するため、発振器分周回路からカウントを加算または減算します。抑制（減算、マイナス校正）または分割（加算、プラス校正）されるパルス数は、0x08 にある校正レジスタの 5 つの校正ビットに格納された値によります。校正ビットは、校正レジスタの 5 つの下位ビットを占有します。これらのビットは、バイナリ形式で「0」と 31 間の任意の値を表すために設定されます。ビット D5 は符号ビットで、「1」がプラス校正、「0」がマイナス校正を示します。カウントを加算するとクロックが速くなり、減算するとクロックが遅くなります。二進数の「1」がレジスタにロードされると、符号に応じて、発振器の誤差に 4.068 または -2.034 ppm のオフセット調整を行います。

校正は、64 分サイクル内で発生します。サイクルの最初の 62 分は、毎分 1 回、128 の発振器サイクルで 1 秒短縮されるか、256 の発振器サイクルで 1 秒長くなります。二進数の「1」がレジスタにロードされると、64 分サイクルの最初の 2 分のみが変更されます。二進数の 6 がロードされると、最初の 12 が影響を受け、同じパターンが続きます。したがって、各校正の手順は、実際の 125,829,120 回発振器サイクルごとに、512 を加算または 256 を減算する効果があります。これは、校正レジスタの校正ステップごとに、4.068 または -2.034 ppm の調整を行うことを意味します。

必要な校正を決定するには、フラグレジスタ (0x00) の CAL ビットを「1」に設定する必要があります。これは、512Hz の公称周波数で INT ピンをトグルします。512Hz から測定される任意の偏差は、必要な補正の程度と方向を示します。たとえば、512.01024Hz の読み込みは +20ppm の誤差を示します。したがって、-10 (001010b) の 10 進値を校正レジスタにロードし、この誤差を相殺する必要があります。

**注** 校正レジスタを設定または変更しても、テスト出力周波数には影響しません。

CAL をリセットするには、書き込みビット「W」( フラグレジスタ – 0x00) を「1」に設定し、フラグレジスタへの書き込みをイネーブルにします。CAL に値を書き込み、次に書き込みビットを「0」にリセットし、書き込みをディスエーブルにします。

## アラーム

アラーム機能は、ユーザーがプログラムしたアラームの時間と日付 (レジスタ 0x01-5 に格納されている) の値を、該当する曜日と日付の値と比較します。一致すると、アラーム内部フラグ

(AF) が設定され、アラーム割り込みイネーブル (AIE) ビットが設定されている場合は、割り込みが INT ピンで生成されます。

日付、時間、分、秒という、4 つのアラーム一致フィールドがあります。これらの各フィールドは、フィールドがアラーム一致ロジックで使用されているかどうかを判断するために使用される一致ビットを持ちます。一致ビットが「0」に設定されている場合は、対応するフィールドが一致プロセスで使用されていることを示します。一致ビットに応じて、アラームは、月に一度など特定の頻度で発生します。最小頻度は、毎分 1 回です。一致ビットを選択しない（すべて 1）場合は、一致が必要とされないため、アラームがディスエーブルになることを示します。すべての一致ビット（すべて 0）を選択すると、正確な時間と日付の一致が発生します。

アラームイベントを検出するには、AF フラグを読み込むまたは INT ピンを監視するという 2 つの方法を使用します。0x00 にあるフラグレジスタの AF フラグは、日付や時間の一致が発生したことを示します。一致が発生すると、AF ビットが「1」に設定されます。フラグレジスタを読み込むと、アラーム フラグビット（および他のすべて）がクリアされます。ハードウェア割り込みピンも、アラーム イベントを検出するために使用されることがあります。

これを設定するには、書き込みビット「W」( フラグレジスタ – 0x00) を「1」に設定し、アラームレジスタへの書き込みをイネーブルにします。アラームの値を書き込んだ後、「W」ビットを「0」にクリアし、効力を発します。

**注** CY14X101PA は、アラームフラグと割り込みを適切にオペレーションするため、アラーム一致ビット（アラーム秒レジスタ 0x02 のビット「D7」）を数秒間「0」に設定する必要があります。

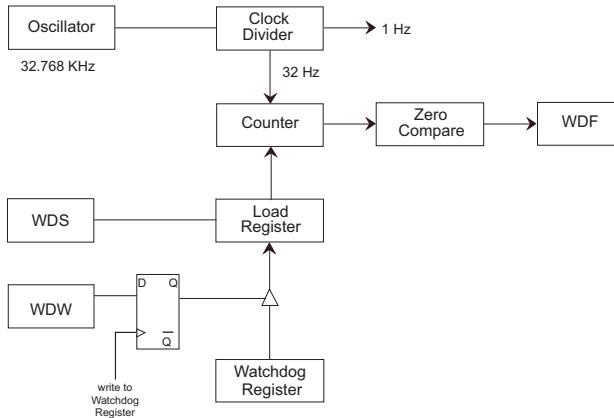

## ウォッチドッグタイマ

ウォッチドッグタイマは、水晶発振器から派生した 32Hz のクロック (31.25ms) を使用する、フリーラン ダウン カウンタです。発振器は、関数へのウォッチドッグとして実行する必要があります。ウォッチドッグ タイマ レジスタにロードされた値からカウント ダウンを開始します。

タイマは、ロード可能なレジスタとフリーランカウンタで構成されています。パワーアップ時に、レジスタ 0x07 のウォッチドッグタイムアウト値が、カウンタのロードレジスタにロードされます。カウントは、ウォッチドッグストローブ (WDS) ビットが「1」に設定されるたびに、ロード可能な値からのパワーアップと再起動を開始します。カウンタは、「0」のピン値と比較されます。カウンタがこの値に達すると、内部フラグとオプションの割り込み出力が発生します。カウンタが「0」に到達する前に WDS ビットを「1」に設定することにより、割り込みタイムアウトを防ぐことができます。これにより、カウンタにウォッチドッグタイムアウト値がロードされ、再起動されます。カウンタがピンの値に達する前に WDS ビットを設定する限り、割り込みとウォッチドッグ タイマフラグは発生しません。

ウォッチドッグ書き込みビットを「0」に設定することで、新しいタイムアウト値が書き込まれます。WDW が「0」である場合、ウォッチドッグタイムアウト値ビット D5-D0 への新しい値の書き込みが有効になり、タイムアウト値が変更されます。WDW が「1」である場合、D5-D0 ビットへの書き込みは無視されます。WDW 機能は、ウォッチドッグタイマの値が変更されることを考慮せずに、WDS ビットを設定できるようにします。ウォッチドッグ タイマの論理 ダイヤグラムを、[23 ページの図 30](#) に示します。ウォッチドッグタイムアウト値を「0」に設定すると、ウォッチドッグ機能がディスエーブルになることに注意してください。

ウォッチドッグ タイマの出力は、ウォッチドッグがタイムアウトまで許可されている場合に設定されるフラグビット WDF です。割り込みレジスタのウォッチドッグ割り込み有効 (WIE) ビットが設定されている場合は、INT ピンのハードウェア割り込みも、ウォッチドッグタイムアウトで生成されます。フラグおよびハードウェア割り込みは、ユーザーがフラグレジスタを読み込んだ時に両方クリアされます。

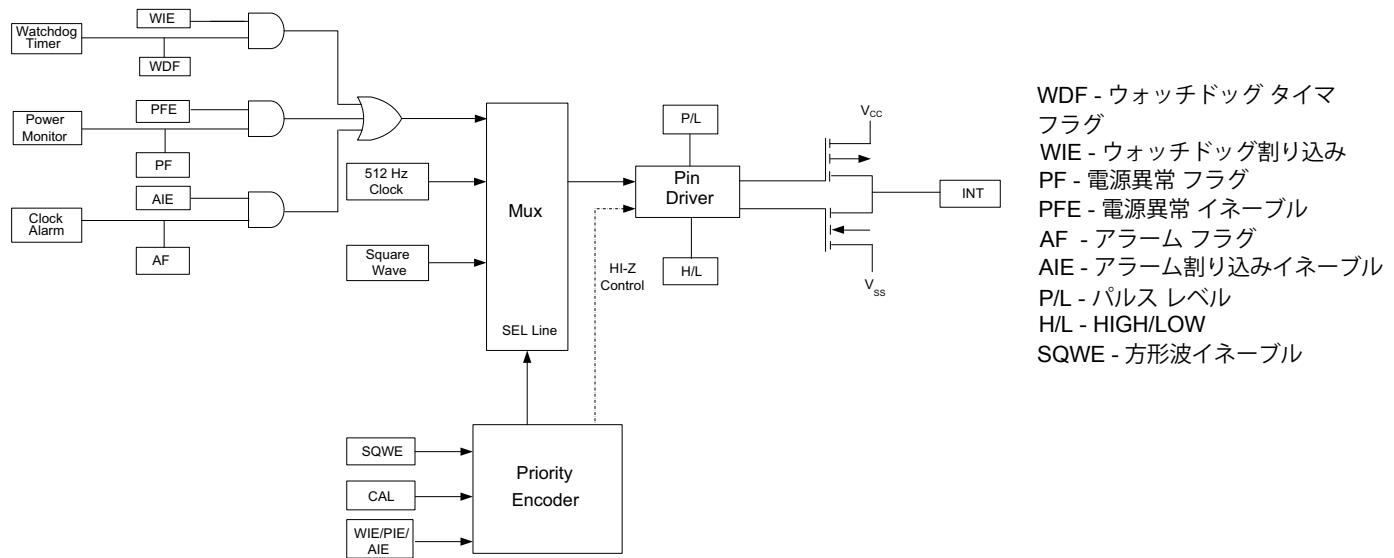

**図 30. ウォッチドッグ タイマ ブロックダイヤグラム**

### プログラマブル方形波ジェネレータ

方形波ジェネレータブロックは、デバイスの INT ピンに所望の周波数を生成するために水晶出力を使用します。出力周波数は、以下のいずれかになるようにプログラムすることができます。

1. 1Hz

2. 512Hz

3. 4096Hz

4. 32768Hz

デバイスがバックアップ電源で実行されている時は、方形波出力は生成されません。

### 電源モニタ

CY14X101PA は、電源異常割り込み機能による電力管理機能を提供します。また、クロック用のバックアップ電源への内部スイッチを制御し、低 V<sub>CC</sub> アクセスからメモリを保護します。電源モニタは、V<sub>CC</sub> 電圧を V<sub>SWITCH</sub> しきい値と比較する、内部バンドギャップ参照回路に基づきます。

[4 ページの AutoStore 処理](#) で説明したように、V<sub>CC</sub> が電源を喪失した際に V<sub>SWITCH</sub> に達すると、データ STORE オペレーションが、SRAM から不揮発性素子に対して開始され、最後の SRAM データ状態を確保します。また、電源が V<sub>CC</sub> からバックアップ電源（バッテリまたはコンデンサ）に切り替えられ、RTC 発振器を処理します。

バックアップ電源から動作している場合、nvSRAM との読み込みおよび書き込みオペレーションが抑制され、RTC 機能が利用できなくなります。RTC クロックは、バックグラウンドで処理を継続します。更新された RTC 時間保持レジスタは、V<sub>CC</sub> が回復された後で利用できるようになります（[35 ページの AutoStore またはパワーアップ RECALL を参照](#)）。

### バックアップ電源モニタ

CY14X101PA は、バックアップ電源（バッテリまたはコンデンサバックアップ）障害を検出するバックアップ電源監視システムを提供します。バックアップ電源に障害が発生した場合、次のパワーアップでバックアップ電源障害フラグ (BPF) が発行されます。バックアップ電圧が V<sub>BAKFAIL</sub> よりも下がった場合に、BPF フラグが設定されます。RTC がバックアップモードで実行中である際もバックアップ電源が監視されます。バックアップモード中に検出された低電圧は、BPF フラグを通してフラグが立てられます。BPF がデータを保持することができる原因是、バックアップ電圧の定義された低レベルまでです (V<sub>DRL</sub>)。

### 割り込み

CY14X101PA は、フラグレジスタ、割り込みレジスタ、およびマイクロコントローラへの割り込み信号を送ることができるロジックを持っています。割り込みには、ウォッチドッグタイマ、電源モニタ、アラーム タイマという 3 つの潜在的ソースがあります。それぞれ、個別に割り込みレジスタ (0x06) の適切な設定によって、INT ピンを駆動するために有効にできます。さらに、ホストプロセッサが割り込みの原因を判別するために使用するフラグレジスタ (0x00) に、関連するフラグビットがあります。INT ピンのドライバは、割り込みが発生したときにその動作を指定する 2 つのビットを持っています。

割り込みは、両方のフラグが、3 つのソースのいずれかによつてオンになった場合、および割り込みレジスタで該当する割り込み有効ビット（「1」に設定）がイネーブルになった場合にのみ発生します。割り込みソースがアクティブになった後、2 つのプログラマブルビット、H/L と P/L は、INT ピンで出力ピンドライバの動作を決定します。これらの 2 ビットは割り込みレジスタにあり、INT ピンからレベルまたはパルスモードの出力を駆動するために使用できます。パルスモードでは、パルス幅が内部で約 200ms に固定されます。このモードは、ホストマイクロコントローラをリセットするためのモードです。レベルモードでは、フラグレジスタがユーザーによって読み込まれるまで、ピンはアクティブ極性になります。このモードは、ホストマイクロコントローラへの割り込みとして使用されます。制御ビットについては、[割り込みレジスタ](#) のセクションで説明されています。

割り込みは、通常の電源による動作中にのみ生成され、システムがバックアップ電源モードで実行されているときにはトリガされません。

**注** CY14X101PA は、電源オン RECALL シーケンスが完了した後でのみ有効な割り込みを生成します。INT ピンの全イベントは、パワーアップ後、t<sub>FA</sub> 中は無視される必要があります。

### 割り込みレジスタ

ウォッチドッグ割り込みの有効化 (WIE) :「1」に設定すると、ウォッチドッグ タイマは、ウォッチドッグ タイムアウトが発生した際に INT ピンと内部フラグを駆動します。WIE を「0」に設定すると、ウォッチドッグ タイマは、フラグ レジスタの WDF フラグにのみ影響します。

アラーム割り込み有効 (AIE) :「1」に設定すると、アラームの一一致により、INT ピンと内部フラグが駆動されます。AIE を「0」に設定すると、アラームの一一致は、フラグ レジスタの AF フラグにのみ影響します。

電源異常割り込み有効 (PFE) :「1」に設定すると、電源異常 モニタにより、ピンと内部フラグが駆動されます。PFE を「0」に設定すると、電源異常 モニタは、フラグ レジスタの PF フラグにのみ影響します。

方形波有効 (**SQWE**)：「1」に設定されると、プログラマブル周波数の方形波が INT ピンに生成されます。周波数は割り込みレジスタの SQ1 と SQ0 ビットによって決定されます。このビットは不揮発性であり、パワーサイクルに耐えます。SQWE ビットは他すべての割り込みよりも優先されます。しかし、CAL ビットは方形波ジェネレータよりも優先されます。このビットのデフォルトは工場出荷時に「0」に設定されています。

**HIGH/LOW (H/L)**：「1」に設定すると、INT ピンがアクティブ HIGH になり、ドライバモードがプッシュ プルになります。INT ピンは、 $V_{CC}$  が  $V_{SWITCH}$  を上回る場合にのみ HIGH を駆動します。「0」に設定すると、INT ピンがアクティブ LOW になり、ドライバモードがオープン ドレインになります。アクティブ LOW モードで割り込みを使用している間、INT ピンは、10 k 抵抗で  $V_{CC}$  にプルアップする必要があります。

**パルス / レベル (P/L)**：「1」に設定し、割り込みが発生すると、INT ピンが約 200 ms 間駆動されます。P/L が「0」に設定されると、INT ピンは、フラグ レジスタが読み込まれるまで、HIGH または LOW (H/L により決定される) に駆動されます。

**SQ1 および SQ0**。SQWE ビットが「1」に設定されている時、これらのビットは INT ピン出力で方形波の周波数を固定するために一緒に使用されます。これらのビットは不揮発性であり、パワーサイクルに耐えます。次の表に示されているように、出力周波数が決定されます。

表 9. SQW 出力選択

| SQ1 | SQ0 | 周波数     | 備考          |

|-----|-----|---------|-------------|

| 0   | 0   | 1Hz     | 1Hz 信号      |

| 0   | 1   | 512Hz   | 校正に便利       |

| 1   | 0   | 4096Hz  | 4kHz クロック出力 |

| 1   | 1   | 32768Hz | 発振器出力周波数    |

イネーブルな割り込みソースが INT ピンをアクティブ化すると、外部ホストはレジスタのフラグを読み込んで、原因を特定

します。レジスタが読み込まれる際には、すべてのフラグがクリアされることに注意してください。INT ピンがレベル モードにプログラムされている場合、条件はクリアされ、INT ピンは非アクティブ状態に戻ります。ピンがパルスモードにプログラムされている場合、フラグの読み取りによってもフラグとピンがクリアされます。フラグ レジスタが読み込まれると、パルスは、その指定された期間を完了しません。INT ピンがホストのリセットとして使用されている場合は、フラグ レジスタはリセット時に読み込まれません。

以下は INT ピンの状態をまとめた表です。

表 10. INT ピンの状態

| CAL | SQWE | WIE/AIE/PFE | INT ピン出力 |

|-----|------|-------------|----------|

| 1   | X    | X           | 512Hz    |

| 0   | 1    | X           | 方形波出力    |

| 0   | 0    | 1           | アラーム     |

| 0   | 0    | 0           | HI-Z     |

### フラグ レジスタ

フラグ レジスタには、3 つのフラグ ビットがあります。これらは、割り込みを生成するために使用することができる WDF、AF、および PF です。これらのフラグは、ウォッチドッグタイムアウト、アラーム一致、または電源異常モニタによってそれぞれ設定されます。フラグが設定される際、プロセッサは、このレジスタをポーリングすること、または割り込みをイネーブルにすることができます。これらのフラグは、レジスタが読み込まれると自動的にリセットされます。フラグ レジスタは、パワーアップ時に値 0x00 を使って自動的にロードされます (OSCF ビットを除く。[21ページの 発振器の起動と停止](#)を参照)。

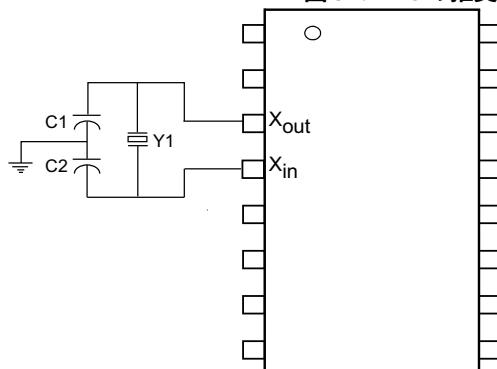

図 31. RTC の推奨コンポーネント構成 [3]

推奨値

$Y_1 = 32.768 \text{ kHz}$  (12.5 pF)

$C_1 = 12 \text{ pF}$

$C_2 = 69 \text{ pF}$

注: C1 と C2 の推奨値はボードトレース静電容量を含みます。

図 32. 割り込みブロック ダイヤグラム

注

3. nvSRAMRTC の設計ガイドラインおよびベストプラクティスについては、アプリケーションノート AN61546 を参照してください。

**表 11. RTC レジスタマップ<sup>[4, 5]</sup>**

| レジスタ | BCD 形式のデータ   |                |                  |                     |                    |         |         |         | 機能 / 範囲                |  |  |  |  |  |  |  |

|------|--------------|----------------|------------------|---------------------|--------------------|---------|---------|---------|------------------------|--|--|--|--|--|--|--|

|      | D7           | D6             | D5               | D4                  | D3                 | D2      | D1      | D0      |                        |  |  |  |  |  |  |  |

| 0x0F | 年 (10 年の位)   |                |                  |                     | 年                  |         |         |         | 年 : 00–99              |  |  |  |  |  |  |  |

| 0x0E | 0            | 0              | 0                | 月 (10 ケ月の位)         | 月                  |         |         |         | 月 : 01–12              |  |  |  |  |  |  |  |

| 0x0D | 0            | 0              | 日 (10 日の位)       |                     | 日 (1 日の位)          |         |         |         | 今月の日 : 01–31           |  |  |  |  |  |  |  |

| 0x0C | 0            | 0              | 0                | 0                   | 0                  | 曜日      |         |         | 曜日 : 01–07             |  |  |  |  |  |  |  |

| 0x0B | 0            | 0              | 時間 (10 時間の位)     |                     | 時間                 |         |         |         | 時間 : 00–23             |  |  |  |  |  |  |  |

| 0x0A | 0            | 分 (10 分の位)     |                  |                     | 分 (1 分の位)          |         |         |         | 分 : 00–59              |  |  |  |  |  |  |  |

| 0x09 | 0            | 秒 (10 秒の位)     |                  |                     | 秒                  |         |         |         | 秒 : 00–59              |  |  |  |  |  |  |  |

| 0x08 | OSCEN (0)    | 0              | Cal sign (0)     | 校正 (00000)          |                    |         |         |         | 校正值 <sup>[6]</sup>     |  |  |  |  |  |  |  |

| 0x07 | WDS (0)      | WDW (0)        | WDT (000000)     |                     |                    |         |         |         | ウォッチドッグ <sup>[6]</sup> |  |  |  |  |  |  |  |

| 0x06 | WIE (0)      | AIE (0)        | PFE (0)          | SQWE (0)            | H/L (1)            | P/L (0) | SQ1 (0) | SQ0 (0) | 割り込み <sup>[6]</sup>    |  |  |  |  |  |  |  |

| 0x05 | M (1)        | 0              | アラーム日 (10 日の位)   |                     | アラーム日 (1 日の位)      |         |         |         | アラーム、今月の日 : 01–31      |  |  |  |  |  |  |  |

| 0x04 | M (1)        | 0              | アラーム時間 (10 時間の位) |                     | アラーム時間 (1 時間の位)    |         |         |         | アラーム時間 : 00–23         |  |  |  |  |  |  |  |

| 0x03 | M (1)        | アラーム分 (10 分の位) |                  |                     | アラーム分 (1 分の位)      |         |         |         | アラーム分 : 00–59          |  |  |  |  |  |  |  |

| 0x02 | M (1)        | アラーム秒 (10 秒の位) |                  |                     | アラーム、秒             |         |         |         | アラーム、秒 00–59           |  |  |  |  |  |  |  |

| 0x01 | 世紀 (10 世紀の位) |                |                  |                     | 世紀 (1 世紀の位)        |         |         |         | 世紀 : 00–99             |  |  |  |  |  |  |  |

| 0x00 | WDF          | AF             | PF               | OSCF <sup>[7]</sup> | BPF <sup>[7]</sup> | CAL (0) | W (0)   | R (0)   | フラグ <sup>[6]</sup>     |  |  |  |  |  |  |  |

**注**

4. () は、工場出荷時の値を示します。

5. RTC レジスタの未使用ビットは後の使用のために予約されており、「0」に設定されている必要があります。

6. これは、バイナリ値ではなく、BCD 値です。

7. ユーザーが OSCF と BPF フラグビットをリセットする場合は、フラグレジスタは、 $t_{RTCp}$  時間の後に更新されます。

**表 12. レジスタ マップ詳細**

| 時間管理 - 年                                                                                                                                    |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------|-----------|----|----|----|--|--|--|--|--|--|--|

| 0x0F                                                                                                                                        | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 年 (10 年の位)                                                                                                                      |            |              |            | 年         |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | 年の下位 2 枠の BCD 枠が含まれています。下位ニブル (4 ビット) には、年の値が含まれています。上位ニブル (4 ビット) には、10 単位の年の値が含まれます。各ニブルは 0 から 9 までになります。レジスタの範囲は 0 から 99 です。 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0E                                                                                                                                        | 時間管理 - 月                                                                                                                        |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 0          | 0            | 月 (10ヶ月の位) | 月         |    |    |    |  |  |  |  |  |  |  |

| 月の BCD 枠が含まれています。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 まで動作します。上位ニブル (1 ビット) は、上位桁が含まれており、0 から 1 で動作します。レジスタの範囲は 1 から 12 です。                    |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0D                                                                                                                                        | 時間管理 - 日                                                                                                                        |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 0          | 日 (10 日の位)   |            | 日 (1 日の位) |    |    |    |  |  |  |  |  |  |  |

| 今月の日の BCD 枠が含まれています。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 まで動作します。上位ニブル (2 ビット) は、上位桁が含まれており、0 から 3 で動作します。レジスタの範囲は 1 から 31 です。うるう年は自動的に調整されます。 |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0C                                                                                                                                        | 時間管理 - 曜日                                                                                                                       |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 0          | 0            | 0          | 0         | 曜日 |    |    |  |  |  |  |  |  |  |

| 下位ニブル (3 ビット) は、曜日に関連する値が含まれます。曜日は、1 から 7 までカウントしてから 1 に戻るリング カウンタです。曜日は日付と統合されていないため、ユーザが、曜日の値に意味を割り当てる必要があります。                            |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0B                                                                                                                                        | 時間管理 - 時間                                                                                                                       |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 0          | 時間 (10 時間の位) |            | 時間        |    |    |    |  |  |  |  |  |  |  |

| 24 時間形式で時間の BCD 値が含まれます。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 まで動作します。上位ニブル (2 ビット) は、上位桁が含まれており、0 から 2 で動作します。レジスタの範囲は 0 から 23 です。             |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0A                                                                                                                                        | 時間管理 - 分                                                                                                                        |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 分 (10 分の位) |              |            | 分 (1 分の位) |    |    |    |  |  |  |  |  |  |  |

| 分の BCD 値が含まれます。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 まで動作します。上位ニブル (3 ビット) は、分の上位の桁が含まれており、0 から 5 で動作します。レジスタの範囲は 0 から 59 です。                   |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x09                                                                                                                                        | 時間管理 - 秒                                                                                                                        |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | 0                                                                                                                               | 秒 (10 秒の位) |              |            | 秒         |    |    |    |  |  |  |  |  |  |  |

| 秒の BCD 値が含まれます。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 まで動作します。上位ニブル (3 ビット) は、上位桁が含まれており、0 から 5 で動作します。レジスタの範囲は 0 から 59 です。                      |                                                                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x08                                                                                                                                        | 校正 / 制御                                                                                                                         |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                                             | D7                                                                                                                              | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                                             | OSCEN                                                                                                                           | 0          | 校正符号         |            | 校正        |    |    |    |  |  |  |  |  |  |  |

| OSCEN                                                                                                                                       | 発振器有効。「1」にセットすると、発振器を停止させます。「0」にクリアすると、発振器を起動します。発振器を停止させると、保存中にバッテリやコンデンサの電力を節約できます。                                           |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 校正符号                                                                                                                                        | タイムベースへの加算 (1) またはタイムベースからの減算 (0) として校正を適用するかどうかを決定します。                                                                         |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 校正                                                                                                                                          | これらの 5 ビットは、クロックの校正を制御します。                                                                                                      |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

**表 12. レジスタ マップ詳細 (つづき)**

| 0x07                                     | ウォッチドッグタイマ                                                                                                                                                                                                                                              |     |                  |      |                 |     |     |     |  |  |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|------|-----------------|-----|-----|-----|--|--|--|--|--|--|

|                                          | D7                                                                                                                                                                                                                                                      | D6  | D5               | D4   | D3              | D2  | D1  | D0  |  |  |  |  |  |  |

|                                          | WDS                                                                                                                                                                                                                                                     | WDW |                  |      |                 |     |     | WDT |  |  |  |  |  |  |

| WDS                                      | ウォッチドッグストローブ。このビットを「1」にセットすると、ウォッチドッグ タイマが再起動されます。このビットを「0」にクリアしても何の影響もありません。ウォッチドッグ タイマをリセットした後、ビットは自動的にクリアされます。WDS ビットは書き込み専用です。これを読み込むと常に「0」が返されます。                                                                                                  |     |                  |      |                 |     |     |     |  |  |  |  |  |  |

| WDW                                      | ウォッチドッグ書き込み有効。このビットを「1」に設定すると、ウォッチドッグタイムアウト値(D5-D0)への全書き込みがディスエーブルになります。これにより、ユーザーはタイムアウト値を変更することなく、ウォッチドッグストローブのビットを設定できるようにします。このビットを「0」にクリアすると、次の書き込みサイクルが完了した際に、ビット D5-D0 がウォッチドッグに書き込まれます。この関数の詳細は、 <a href="#">22 ページの ウォッチドッグ タイマ</a> に説明されています。 |     |                  |      |                 |     |     |     |  |  |  |  |  |  |

| WDT                                      | ウォッチドッグタイムアウトの選択。ウォッチドッグ タイマの間隔は、このレジスタの 6 ビットの値によって選択されます。それは、32Hz カウント (31.25ms) の乗数を表します。タイムアウト値の範囲は、31.25ms(「1」の設定)から 2 秒(3FH の設定)です。ウォッチドッグタイマレジスタを「0」にクリアすると、タイマがディスエーブルになります。WDW ビットが前のサイクルで 0 に設定されている場合にのみ、これらのビットを書き込むことができます。                |     |                  |      |                 |     |     |     |  |  |  |  |  |  |

| 0x06                                     | 割り込みステータス / 制御                                                                                                                                                                                                                                          |     |                  |      |                 |     |     |     |  |  |  |  |  |  |

|                                          | D7                                                                                                                                                                                                                                                      | D6  | D5               | D4   | D3              | D2  | D1  | D0  |  |  |  |  |  |  |

|                                          | WIE                                                                                                                                                                                                                                                     | AIE | PFE              | SQWE | H/L             | P/L | SQ1 | SQ0 |  |  |  |  |  |  |

| WIE                                      | ウォッチドッグ割り込み有効。「1」にセットし、ウォッチドッグ タイムアウトが発生すると、ウォッチドッグ タイマが INT ピンと WDF フラグを駆動します。「0」にクリアすると、ウォッチドッグ タイムアウトは、WDF フラグにのみ影響を与えます。                                                                                                                            |     |                  |      |                 |     |     |     |  |  |  |  |  |  |